|

23 |

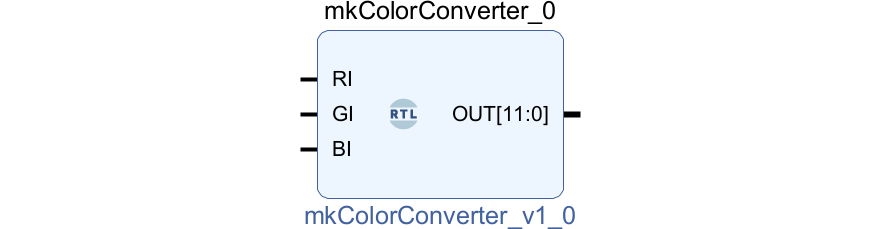

色変換回路 (5) |

|

BSVフォーラムで議論したところ、以下のような回答を順次頂きました。

- 最初の一括でリターンを返すメソッドのほうが良い。が、メソッドの構造体を分割する手段は現状のBSVの文法にはない。従って手段としては2つあり、外側にverilogラッパーを設けて分割するか、BSVに新たな機能を追加するか。

- 組み合わせ回路の関数を置いたらどうか?

- clockとresetは、インタフェース外の端子を使えば消すことができる。

- RDYが1にもかかわらずエラーになる件はbscのissueとして登録した。

組み合わせ回路の関数は良い方法だと思うので、今後色変換回路を組み込む場合にはそうしようと思います。

しかしながら今回は外付けのモジュールとしたため、clockとresetを消去する方法で行きたいと思います。提示されたソースは以下のとおり。

interface ColorConverter;

(* result="RO" *)

method Bit#(4) getRO();

(* result="GO" *)

method Bit#(4) getGO();

(* result="BO" *)

method Bit#(4) getBO();

endinterface

(* synthesize, always_ready, no_default_clock, no_default_reset *)

module mkColorConverter(

(* port="RI" *) Bit#(1) r,

(* port="GI" *) Bit#(1) g,

(* port="BI" *) Bit#(1) b,

ColorConverter ifc);

method Bit#(4) getRO();

return (case ({r, g, b})

3'b000: 4'h0;

3'b001: 4'h9;

3'b010: 4'hd;

3'b011: 4'h5;

3'b100: 4'hc;

default: 4'h0;

endcase);

endmethod

method Bit#(4) getGO();

return (case ({r, g, b})

3'b000: 4'h0;

3'b001: 4'h4;

3'b010: 4'h8;

3'b011: 4'hb;

3'b100: 4'hc;

default: 4'h0;

endcase);

endmethod

method Bit#(4) getBO();

return (case ({r, g, b})

3'b000: 4'h0;

3'b001: 4'h1;

3'b010: 4'h4;

3'b011: 4'h5;

3'b100: 4'hC;

default: 4'h0;

endcase);

endmethod

endmodule

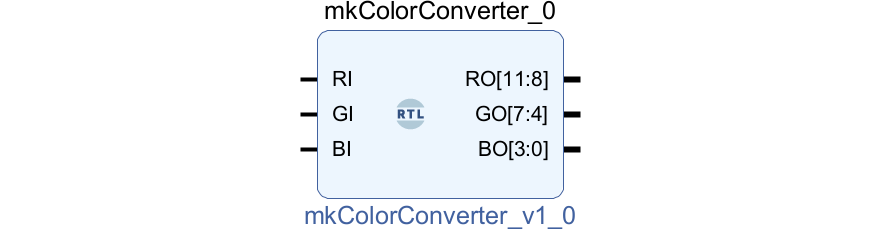

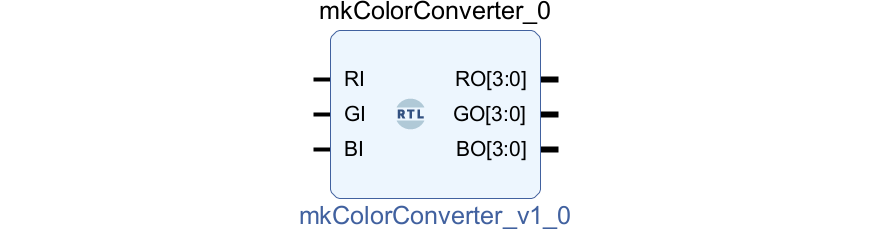

メソッドを用いない入力方法があるようです。具体的にはinterfaceはメソッドを並べるため、interface定義外にポートを定義しています。

また、カラー0は非表示画面も示すため、変換せずに0のままと変更しました。

このソースから生成されるverilogコードはヘッダや定義文を除いて次のとおり。

module mkColorConverter(RI,

GI,

BI,

RO,

GO,

BO);

input RI;

input GI;

input BI;

// value method getRO

output [3 : 0] RO;

// value method getGO

output [3 : 0] GO;

// value method getBO

output [3 : 0] BO;

// signals for module outputs

reg [3 : 0] BO, GO, RO;

// remaining internal signals

wire [2 : 0] x__h151;

// value method getRO

always@(x__h151)

begin

case (x__h151)

3'b0: RO = 4'h0;

3'b001: RO = 4'h9;

3'b010: RO = 4'hD;

3'b011: RO = 4'h5;

3'b100: RO = 4'hC;

default: RO = 4'h0;

endcase

end

// value method getGO

always@(x__h151)

begin

case (x__h151)

3'b0: GO = 4'h0;

3'b001: GO = 4'h4;

3'b010: GO = 4'h8;

3'b011: GO = 4'hB;

3'b100: GO = 4'hC;

default: GO = 4'h0;

endcase

end

// value method getBO

always@(x__h151)

begin

case (x__h151)

3'b0: BO = 4'h0;

3'b001: BO = 4'h1;

3'b010: BO = 4'h4;

3'b011: BO = 4'h5;

3'b100: BO = 4'hC;

default: BO = 4'h0;

endcase

end

// remaining internal signals

assign x__h151 = { RI, GI, BI } ;

endmodule // mkColorConverter

verilogは正しく生成されています。