PL部UARTのPCへの出力

以前Space Invadersのゲーム実行中のVRAM画面の吸出しを実施しました。過去記事ではこれ等が相当します。これは、メモリダンプモジュールをBSVにより設計し、UARTの送信機能を用いてUART/USB変換ボードを経由してPCとUSBで接続し、PC上のPuttyでメモリダンプ情報を取得するというものです。

ところが、再度実行しようとしたところ、どうしてもUARTの出力の取得ができませんでした。前回は比較的簡単にできてしまったので、記事にはpin設定であるxdcの詳細は書いていませんでした。単にUART_TXに接続するとのみと書いており、端子番号は今は定かではありません。

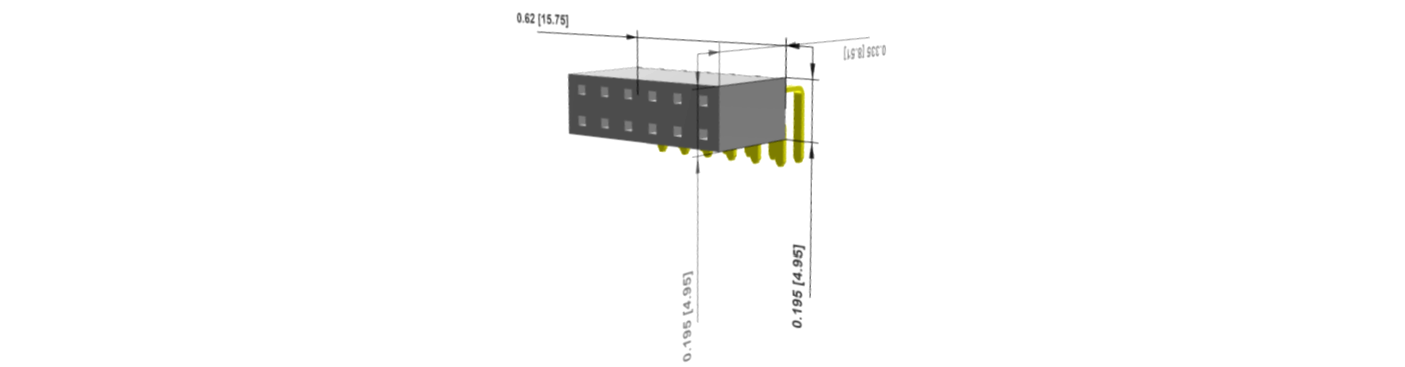

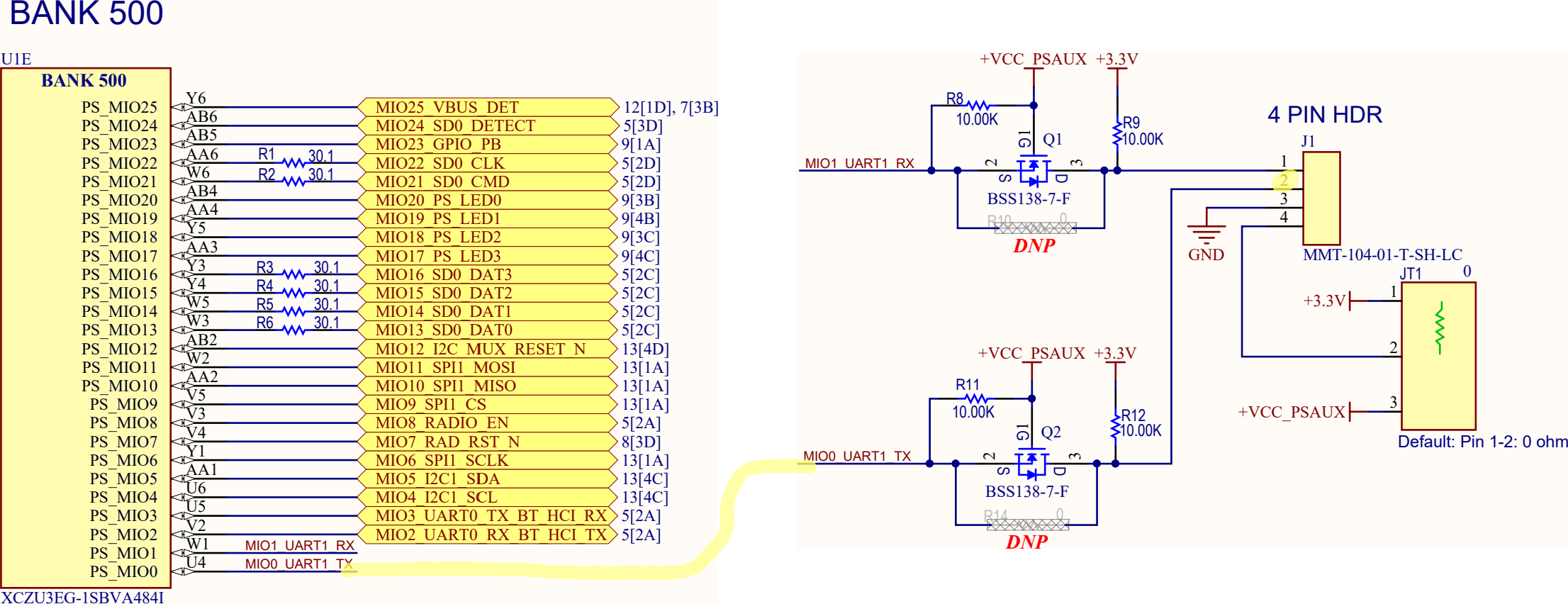

こうなると基本から調べなければならないので、まずUltra96V2の回路図を見ると、なんとPS部からの接続となっているようです。

図605.1 Ultra96 UART部分回路図

図605.1 Ultra96 UART部分回路図

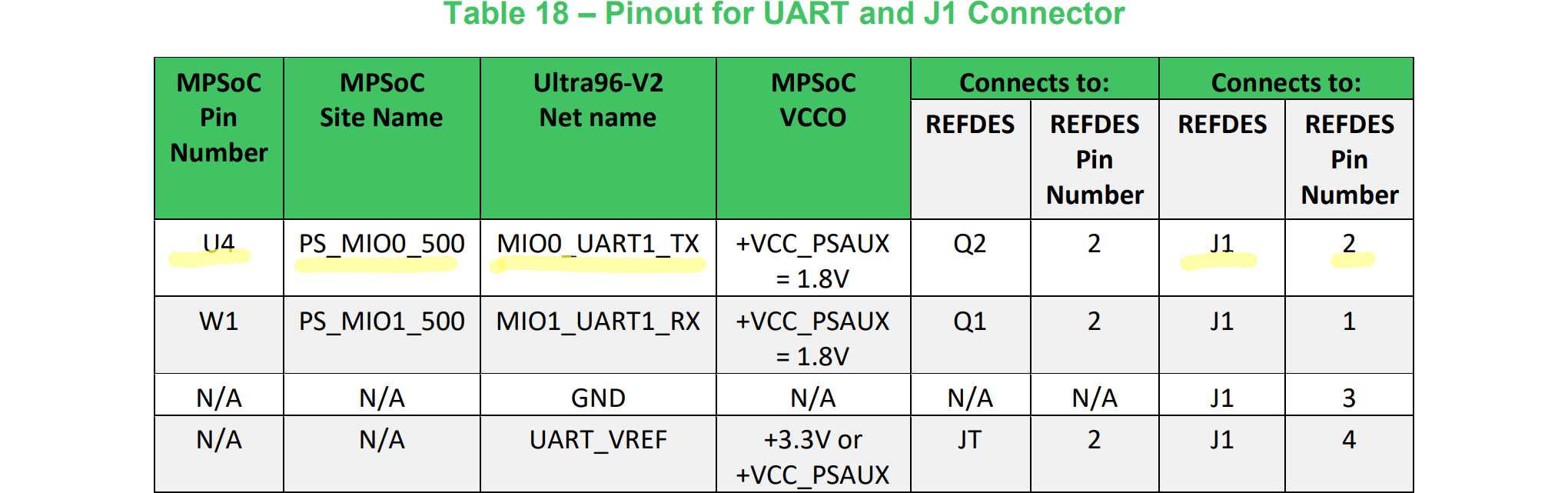

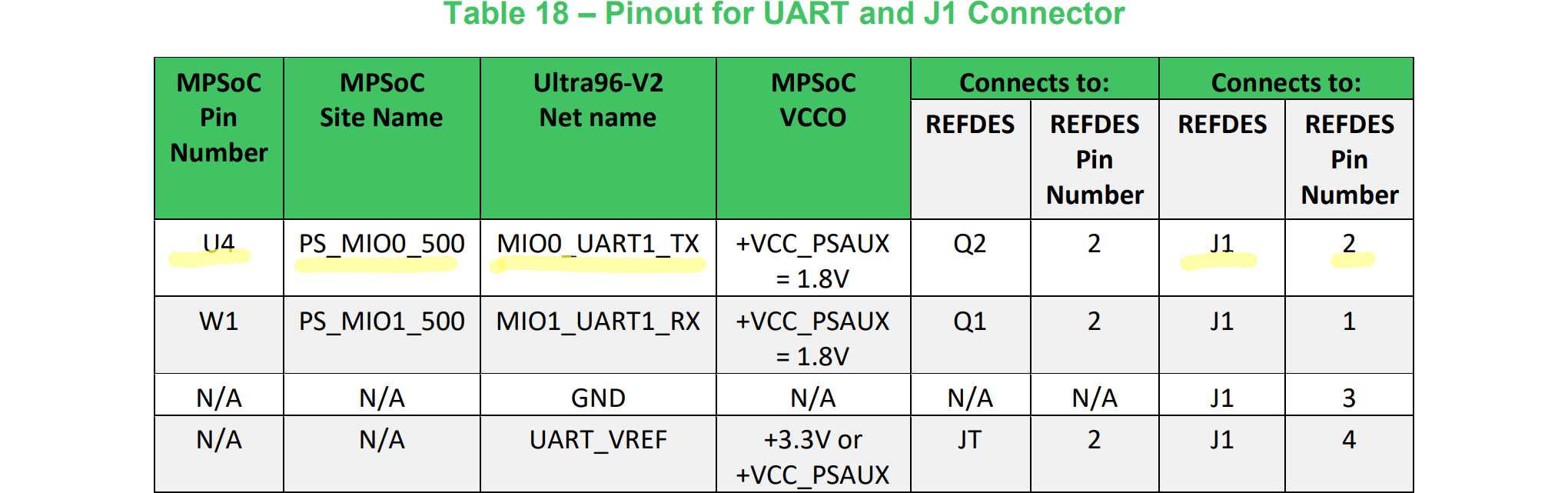

UART/USB変換ボードのJ1の2 pinにUART_TXが接続されていますが、これはPS_MIO0のUART1_TXであり、PLからはPIN配置でエラーになるため、PS部であるBank 500のU4端子に接続することはできません。図605.2にUltra96-V2ハードウェアユーザーズガイドの抜粋を示しますが、やはりBank 500(PS部)のU4端子となっています。

図605.2 Ultra96 UART部分端子表

図605.2 Ultra96 UART部分端子表

従って、最後の手段としてボード上に配線をハンダ付けし無理やりJ1に出力することを考えます。

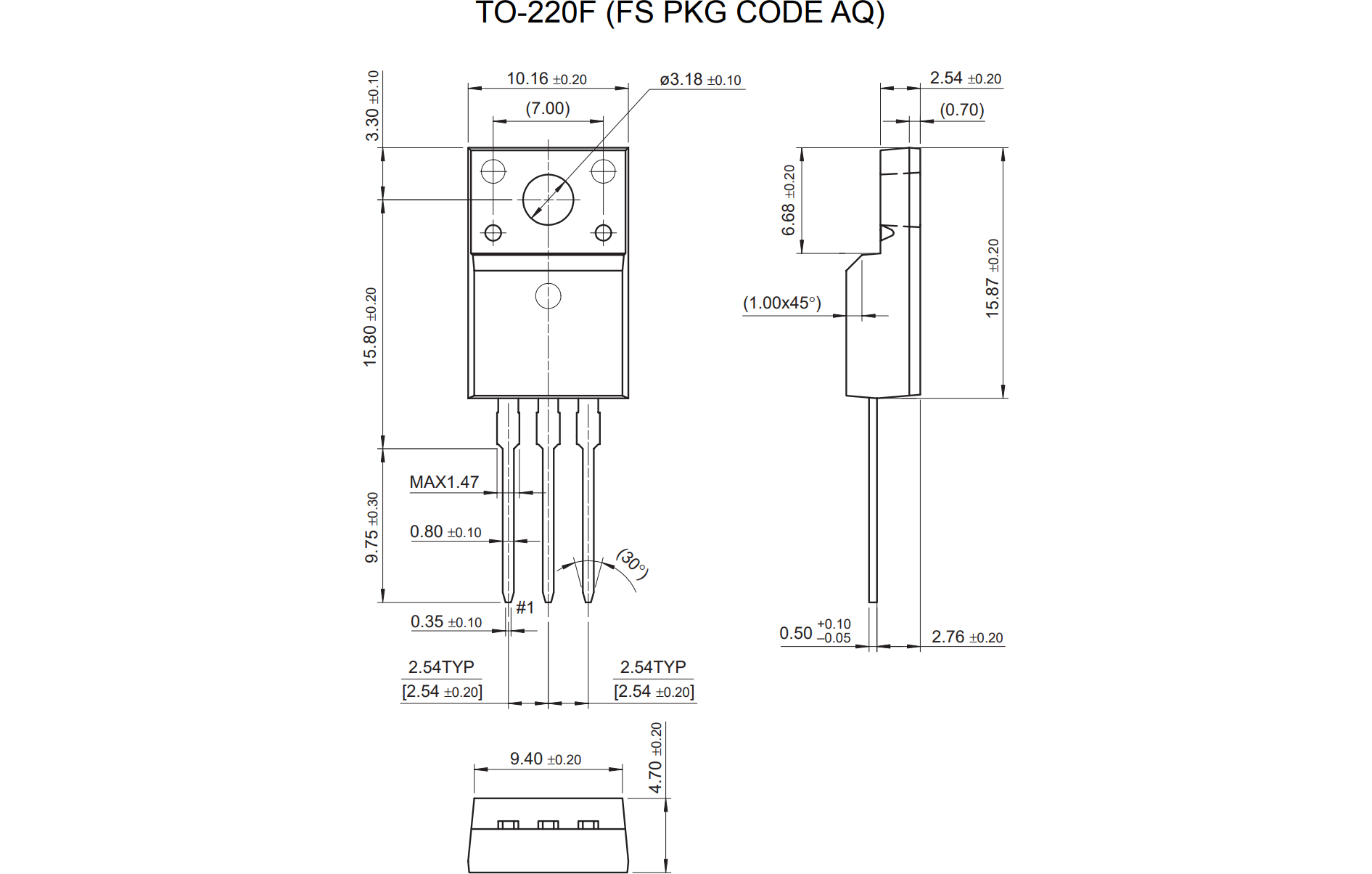

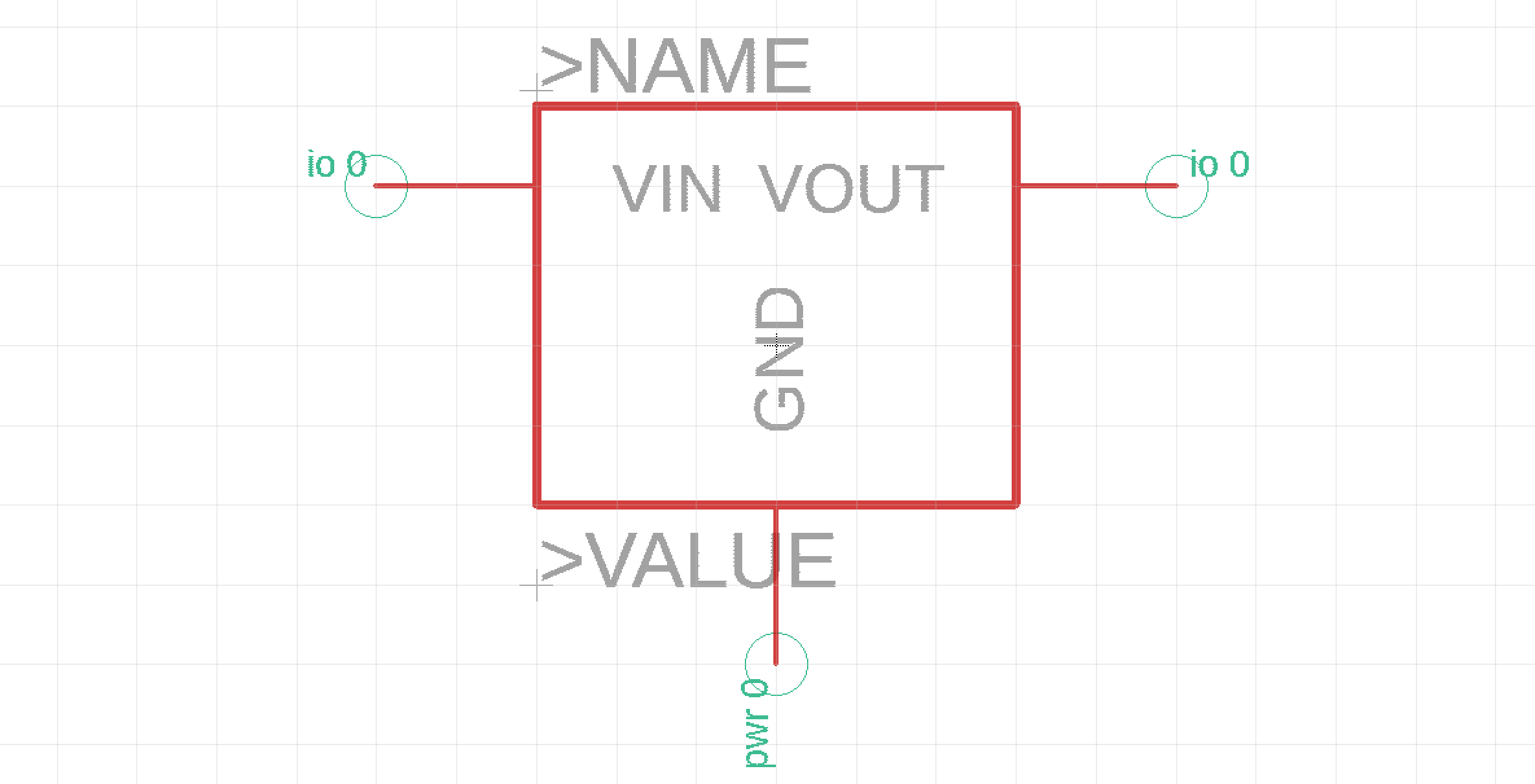

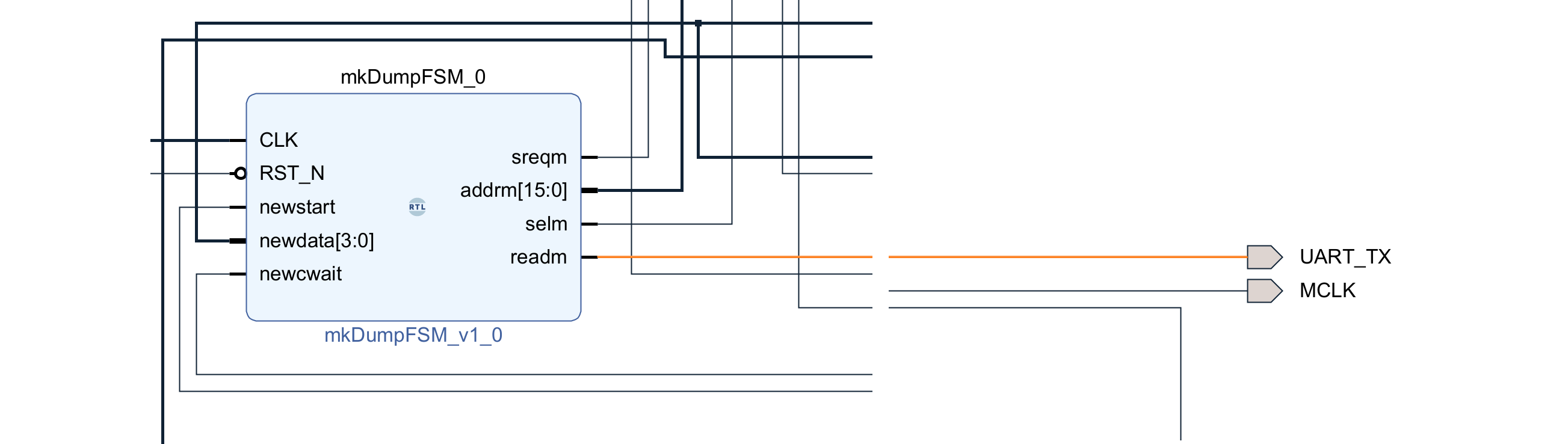

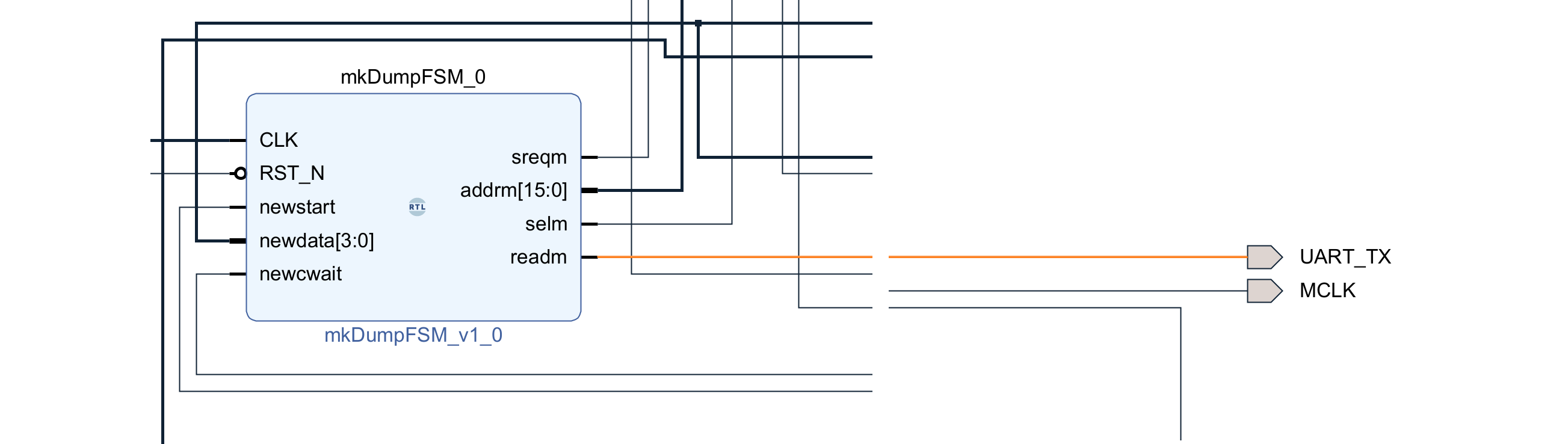

まず図605.3はPL部UART_TXの引き出しを示す回路図です。

図605.3 UART_TX部回路図

図605.3 UART_TX部回路図

このUART_TXを次のxdcによりG6端子に割り当てます。これはPL部の出力(Bank 26)です。

set_property PACKAGE_PIN G6 [get_ports {UART_TX}]

最後にUART_TXを割り着けた端子G6とJ1の2 pinの間に配線をハンダ付けし、ショートしてやります。レベル的に本来はTrのD側ではなくS側に接続すべきですが、3.3Vにpull upされているため、これでもVOHは満足しているようです。

このようにすることで921,600bpsにより、VRAM内容の送信がうまく動作しました。が、以前設定だけでできた理由は不明のままです。

PCへの出力結果の確認

以下に、得られたlogファイルを画像に変換するフィルタを再掲します。

log2ppm.c

#include <stdio.h>

void main() {

char line[4096];

char ch;

printf("P3\n256 256\n255\n");

for(int y = 0; y <= 255; y++) {

fgets(line, sizeof(line), stdin);

for(int x = 0; x <= 255; x++) {

ch = line[x] - 0x30;

if ((ch & 0x4) != 0) printf("255 "); // R

else printf("0 ");

if ((ch & 0x2) != 0) printf("255 "); // G

else printf("0 ");

if ((ch & 0x1) != 0) printf("255 "); // B

else printf("0 ");

}

printf("\n");

}

}

以下のコマンドによりフィルタを作成します。

$ gcc -O log2ppm.c -o log2ppm

これを下記のようにフィルターとして実行し、ログデータを画像ファイルに変換します。

$ ./log2ppm <putty.log >putty.ppm

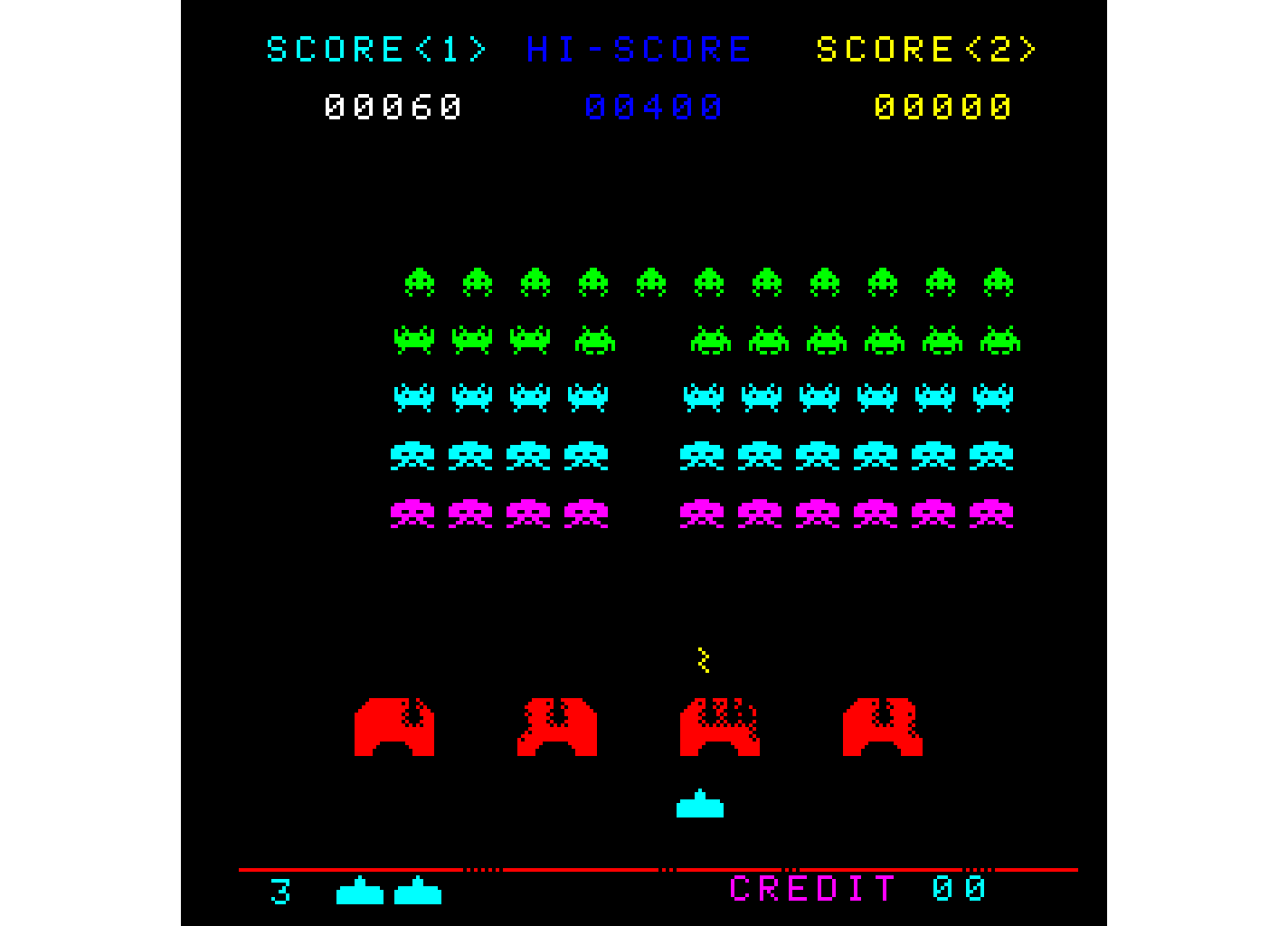

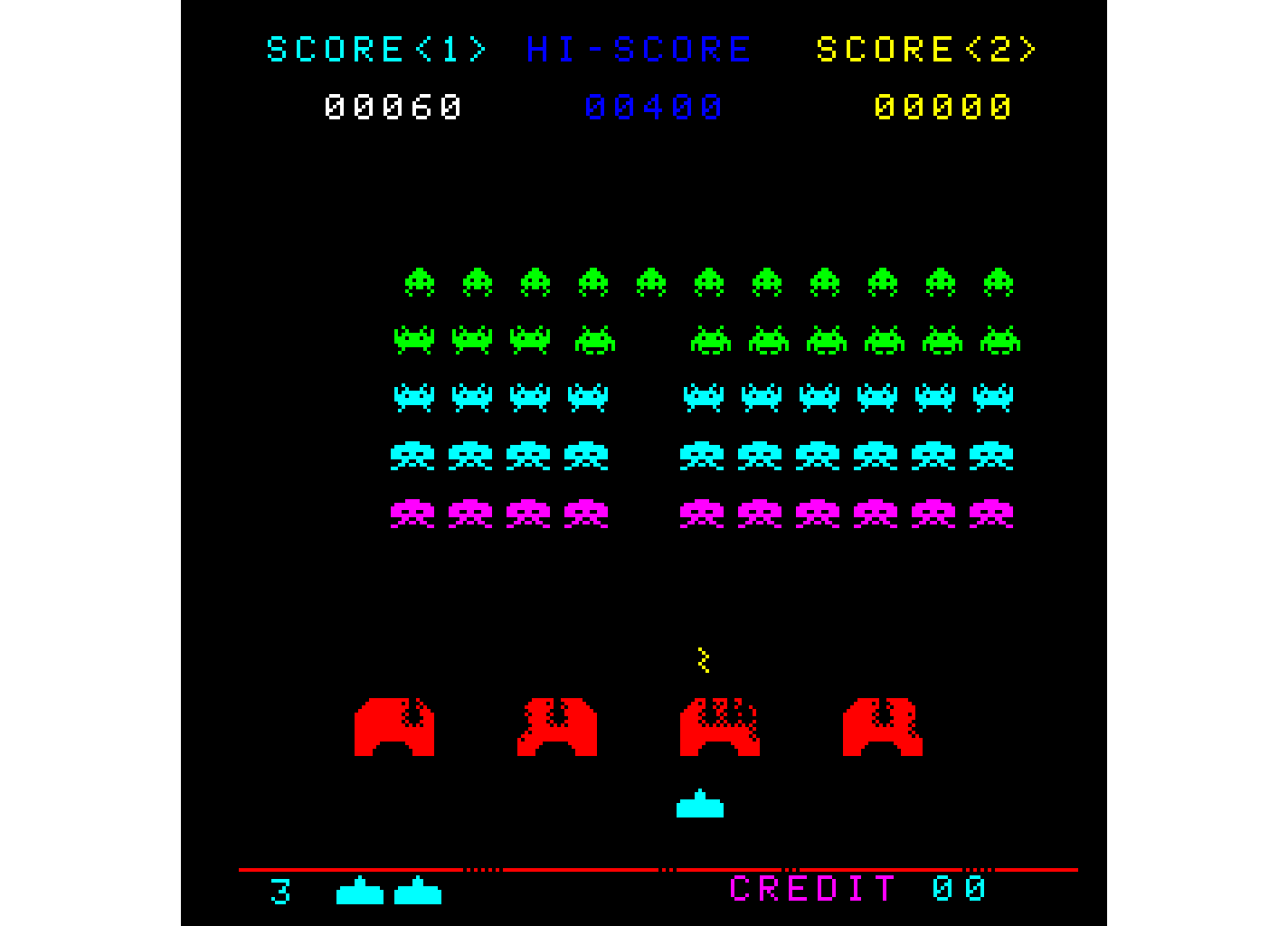

生成されたppm図形を図605.4に示します。

図605.4 メモリダンプ図形

図605.4 メモリダンプ図形

前のブログ

次のブログ

前のブログ

次のブログ