|

16 |

グラフィックディスプレイコントローラの設計 (2) |

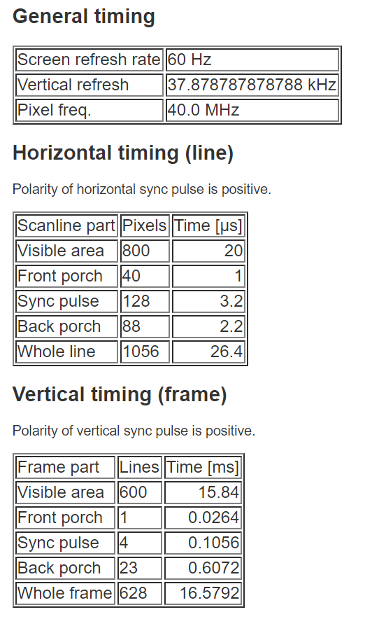

先にご紹介したサイトから得た、SVGAのタイミング表を以下に示します。

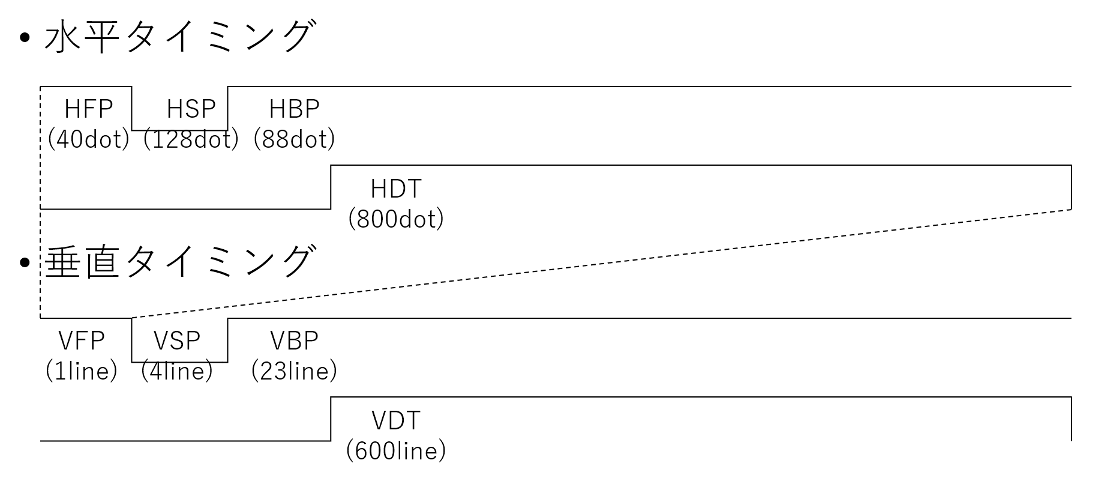

水平タイミングを例にとれば、それぞれHFP, HSP, HBPとなります。トータルでは表示期間であるHDPをすべて加えて、HFP+HSP+HBP+HDP=40+128+88+800=1056が水平期間(26.4us)となり、これをラインと呼びます。水平周波数は37.878787KHzとなります。

垂直タイミングはこのラインがひとつの単位となります。表示期間はVDP=600、その他非表示期間はVFP=1、VSP=4、VBP=23となり、トータルでは628ラインとなります。ラインが集まり一つのフレームを構成し、その周期は16.5792msec、垂直周波数は60.3165412083Hzとなります。

Leave a Comment