|

4 |

BSVによるUARTの設計 (5) |

Verilogシミュレーション

bscにより階層的にverilogファイルを生成し、iverilogによりverilogシミュレーションを行います。さらに波形を観測します。太字は入力文字を示します。

$ bsc -u -verilog Tb.bsv

checking package dependencies

compiling ./Uart.bsv

code generation for mkUart starts

Verilog file created: mkUart.v

compiling Tb.bsv

code generation for mkTb starts

Verilog file created: mkTb.v

All packages are up to date.

$ iverilog top.v mkTb.v mkUart.v -o mkTb

$ ./mkTb

VCD info: dumpfile mkTb.vcd opened for output.

$ gtkwave -A mkTb.vcd

GTKWave Analyzer v3.3.107 (w)1999-2020 BSI

[0] start time.

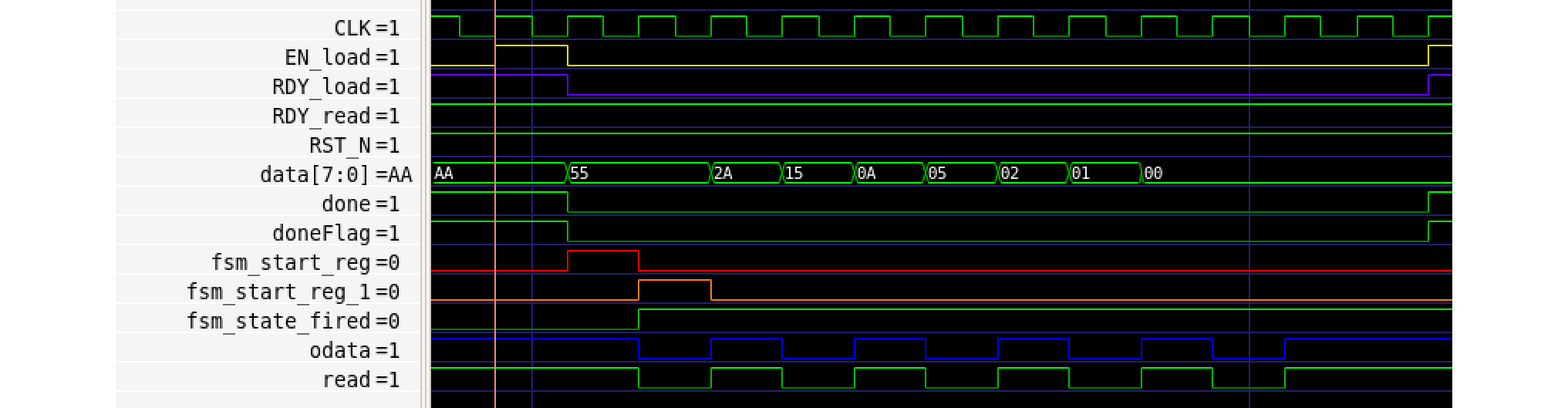

前記事に示すように、データ55H, AAH, C3H, 3CHを順に送信する場合の、モジュールの内部の波形です。

- 最初にデータがAAHになっていますが、BSVでは不定値をAAHで表しています。最初の送信データは55Hです。

- モジュールからRDY_load(青)がアサートされているので、テストベンチからデータが出力されると同時にEN_load(黄)がアサートされます。

- 次に内部レジスタdata(緑)が55Hに変化します。同時にdoneがネゲートされます。同時にFSMの開始レジスタfsm_start_reg(赤)がアサートされます。

- 次にfsm_start_reg_1(赤)がアサートされ、FSMが開始します。そのタイミングでodata(青)のスタートビット(=L)を出力します。

- 次にodata(青)の8bitをLSBから順に10101010と出力します。これはデータが55Hであるためです。

- 最後にストップビット(=H)を2bit出力します。

- 次にdone(緑)がアサートされ、同時にRDY_load(青)がアサートされます。

- 次の送信データはAAHです。

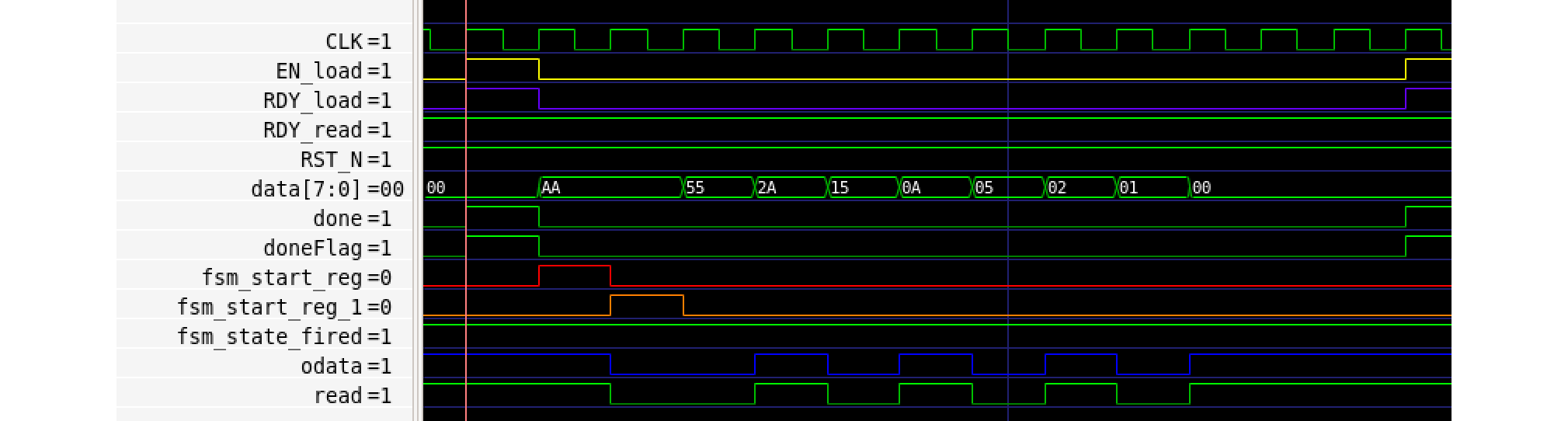

- 次にモジュールからRDY_load(青)がアサートされているので、テストベンチからデータが出力されると同時にEN_load(黄)がアサートされます。

- 次に内部レジスタdata(緑)がAAHに変化します。同時にdoneがネゲートされます。

- 次にFSMの開始レジスタfsm_start_reg(赤)がアサートされます。

- 次にfsm_start_reg_1(赤)がアサートされ、FSMが開始します。そのタイミングでodata(青)のスタートビット(=L)を出力します。

- 次にodata(青)の8bitをLSBから順に01010101と出力します。これはデータがAAHであるためです。

- 最後にストップビット(=H)を2bit出力します。

- 次にdone(緑)がアサートされ、同時にRDY_load(青)がアサートされます。

- 次の送信データはC3Hです。

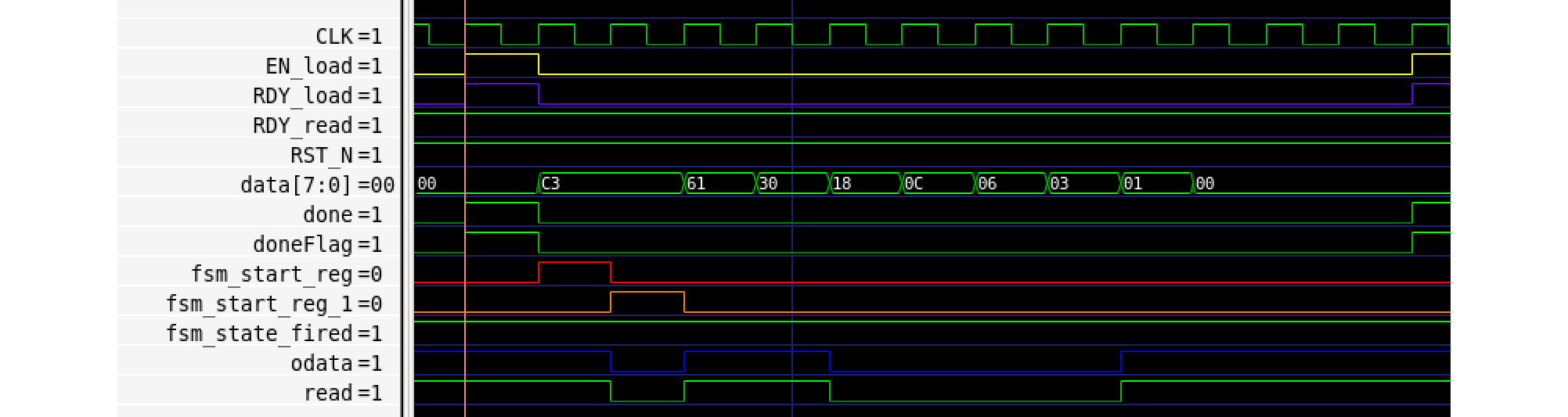

- 次にモジュールからRDY_load(青)がアサートされているので、テストベンチからデータが出力されると同時にEN_load(黄)がアサートされます。

- 内部レジスタdata(緑)がC3Hに変化します。同時にdoneがネゲートされます。同時にFSMの開始レジスタfsm_start_reg(赤)がアサートされます。

- 次にfsm_start_reg_1(赤)がアサートされ、FSMが開始します。そのタイミングでodata(青)のスタートビット(=L)を出力します。

- 次にodata(青)の8bitをLSBから順に11000011と出力します。これはデータがC3Hであるためです。

- 最後にストップビット(=H)を2bit出力します。

- 次にdone(緑)がアサートされ、同時にRDY_load(青)がアサートされます。

- 次の送信データは3CHです。

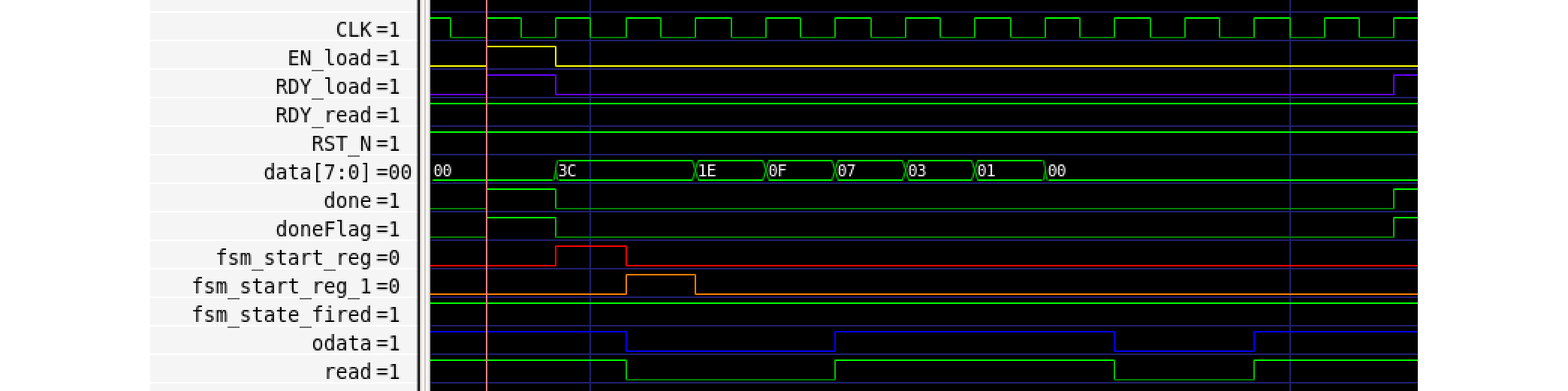

- 次にモジュールからRDY_load(青)がアサートされているので、テストベンチからデータが出力されると同時にEN_load(黄)がアサートされます。

- 次に内部レジスタdata(緑)が3CHに変化します。同時にdoneがネゲートされます。同時にFSMの開始レジスタfsm_start_reg(赤)がアサートされます。

- 次にfsm_start_reg_1(赤)がアサートされ、FSMが開始します。そのタイミングでodata(青)のスタートビット(=L)を出力します。

- 次にodata(青)の8bitをLSBから順に00111100と出力します。これはデータが3CHであるためです。

- 最後にストップビット(=H)を2bit出力します。

- 次にdone(緑)がアサートされ、同時にRDY_load(青)がアサートされます。

- テストベンチはdoneを監視しているので、doneがアサートされると終了です。

Leave a Comment