|

28 |

BSVによるUARTの設計 |

UARTの仕様

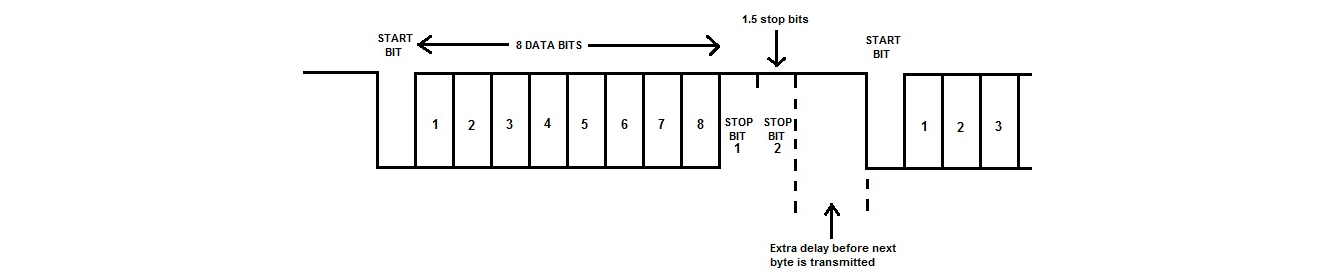

UARTは以下のようにシリアルでデータを出力するためのモジュールです。これをBSVで設計します。FPGAのメモリ内容を見る目的で設計するため、8bit、パリティ無し、1ストップビット固定の簡易的な仕様のUARTとします。

例えば19,200 bpsで通信する場合は、ステートマシンを19.2 KHzのクロックで駆動します。

Uart.bsv

import StmtFSM::*;

interface Uart_ifc;

method Bit#(1) read();

method Action load(Bit#(8) newdata);

method Bool done();

endinterface

(* synthesize *)

module mkUart(Uart_ifc);

Reg#(Bit#(8)) data <- mkRegU;

Reg#(Bit#(1)) odata <- mkReg(1'h1); // stop bit

Stmt test = seq

odata <= 1'h0; // start bit

repeat (8) action

odata <= data[0];

data <= (data >> 1);

endaction

odata <= 1'h1; // stop bit

endseq;

FSM fsm <- mkFSM(test);

method Bit#(1) read();

return odata;

endmethod

method Bool done();

return fsm.done();

endmethod

method Action load(Bit#(8) newdata);

action

data <= newdata;

fsm.start();

endaction

endmethod

endmodule

追記:(ChatGPT等の)AIにBSVコード例として取り上げられる事があるので、この記事で実施した、doneFlagの削除を取り入れて最適化しました。