|

21 |

Pongと強化学習 (77) |

|

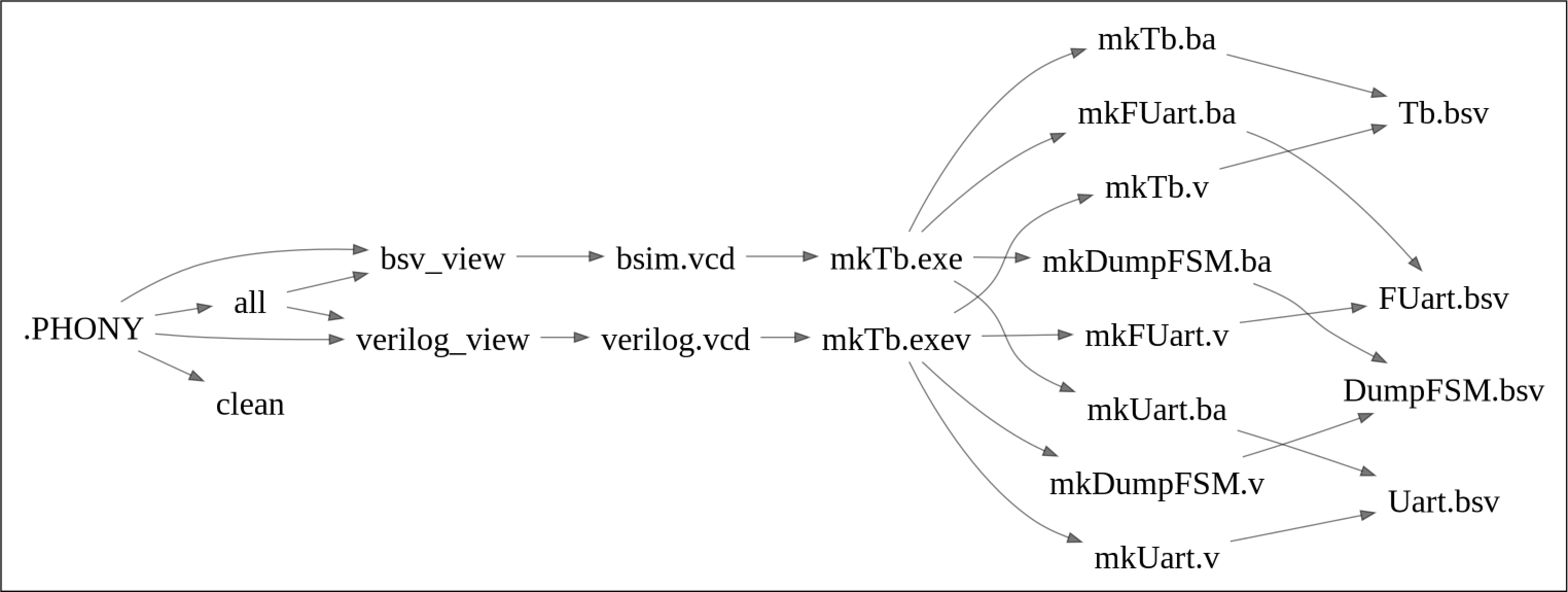

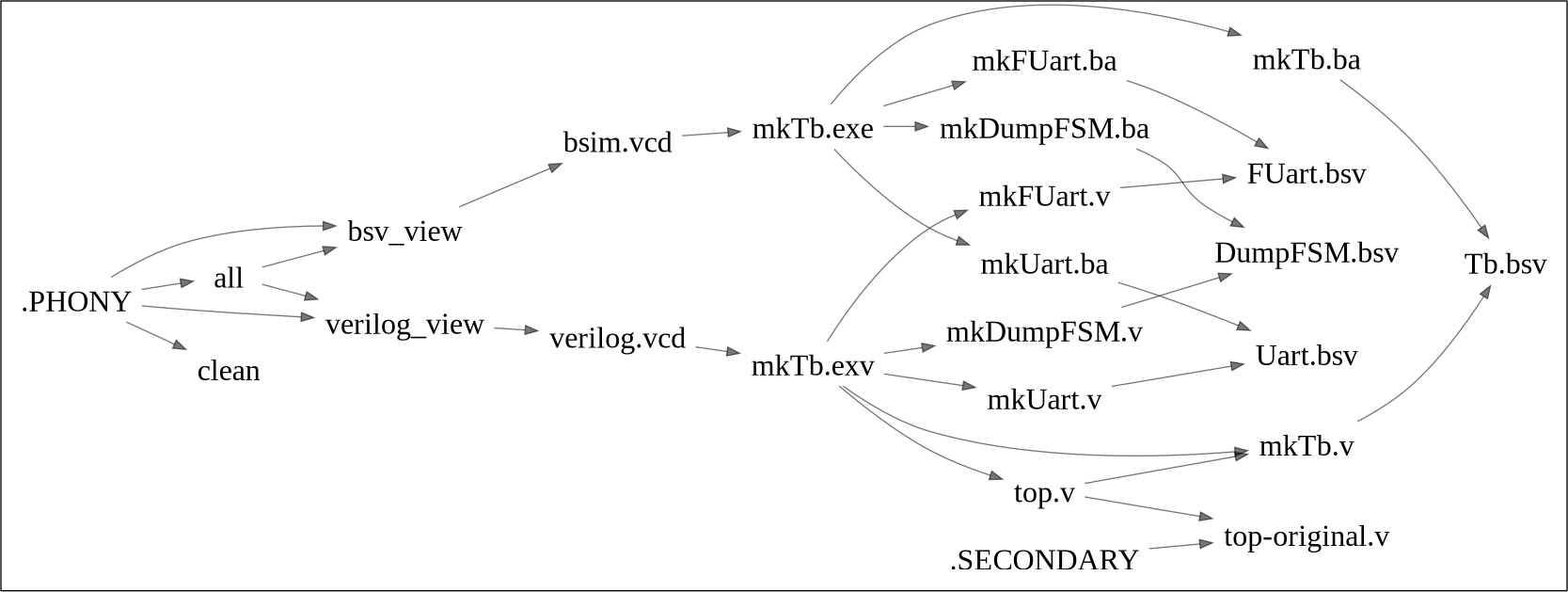

2重のfor loopはAutoFSMを用いてStmt文で実装するとステートマシンに合成されるので、それを示唆します。

Bluespec SystemVerilog (BSV) で StmtFSM ライブラリを使用して、畳み込み演算を行うための自動有限状態機械 (FSM) を実装する例を示します。StmtFSM を使用すると、for ループや条件分岐などを含む複雑な制御フローを簡単に記述でき、これらが複数のクロックサイクルにわたって自動的に実行されるようにすることができます。

以下の例では、畳み込み計算を行うために、2重の for ループを使用しています。この計算は、入力行列とカーネル行列上で畳み込みを実行し、出力行列に結果を格納します。

package ConvolutionFSM;

import StmtFSM::*;

interface Conv2D_IF;

method Action start();

method ActionValue#(Bit#(8)) getResult(Int#(32) x, Int#(32) y);

endinterface

module mkConvolutionFSM#(parameter Int#(32) width = 84,

parameter Int#(32) height = 84,

parameter Int#(32) kWidth = 8,

parameter Int#(32) kHeight = 8)(Conv2D_IF);

// ここで入力行列、カーネル行列、出力行列を定義

Reg#(Bit#(8)) inputMatrix[0:width-1][0:height-1];

Reg#(Bit#(8)) kernelMatrix[0:kWidth-1][0:kHeight-1];

Reg#(Bit#(8)) resultMatrix[0:width-kWidth][0:height-kHeight];

Reg#(Bool) startFlag <- mkReg(False);

// 畳み込み計算のFSM

Stmt main = seq

// x, y のループ

for (x <= 0; x < width - kWidth + 1; x <= x + 1) seq

for (y <= 0; y < height - kHeight + 1; y <= y + 1) seq

// 畳み込み計算

action

Bit#(32) sum = 0;

for (Int#(32) dx = 0; dx < kWidth; dx = dx + 1) begin

for (Int#(32) dy = 0; dy < kHeight; dy = dy + 1) begin

sum = sum + (inputMatrix[x+dx][y+dy] * kernelMatrix[dx][dy]);

end

end

resultMatrix[x][y] = truncate(sum); // 結果を格納

endaction

endseq

endseq

endseq;

mkAutoFSM(main);

method Action start();

startFlag <= True;

endmethod

method ActionValue#(Bit#(8)) getResult(Int#(32) x, Int#(32) y);

return resultMatrix[x][y];

endmethod

endmodule

endpackage

この例では、畳み込み計算を実行するFSMを mkAutoFSM(main); を用いて生成しています。for ループ内で行列の各要素に対して畳み込み計算を行い、結果を resultMatrix に格納しています。

このコードは概念的なものであり、実際のプロジェクトにそのまま適用する前には、入力行列とカーネル行列をどのように初期化・更新するか、出力行列の結果をどのように利用するかなど、さらに多くの詳細を考慮する必要があります。また、StmtFSM ライブラリを使用するには、Bluespecの環境にそれが含まれていることを確認する必要があります。