|

5 |

Lチカの実装 (5) |

Vivadoの操作

実際の操作方法を記述して行きます。

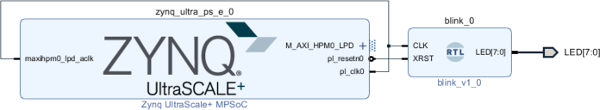

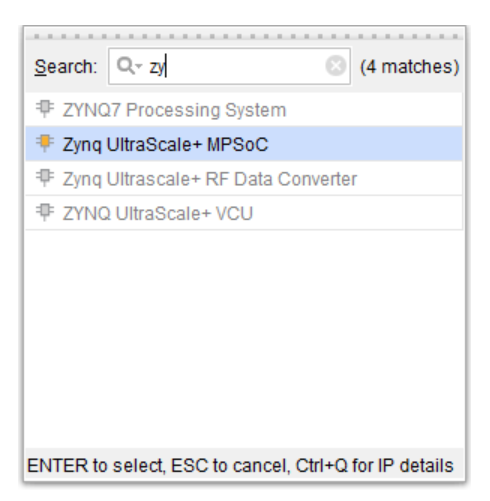

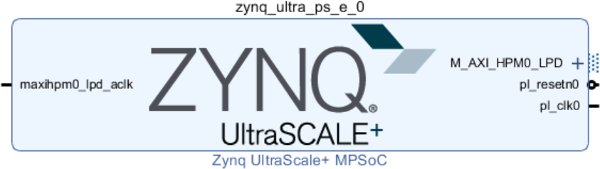

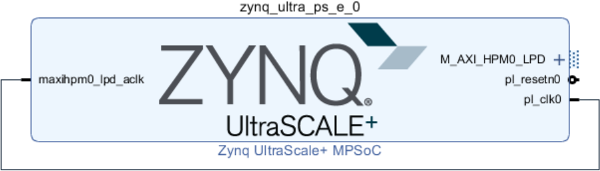

- Zynqブロック作成

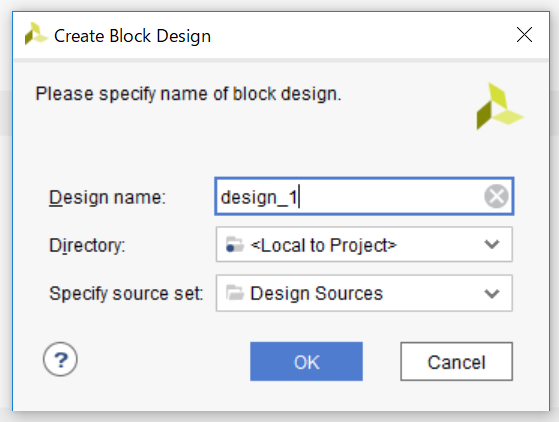

左端のFlow NavigatorよりIP INTEGRATORのCreate Block Designをクリック。以下のメニューでそのままOK。

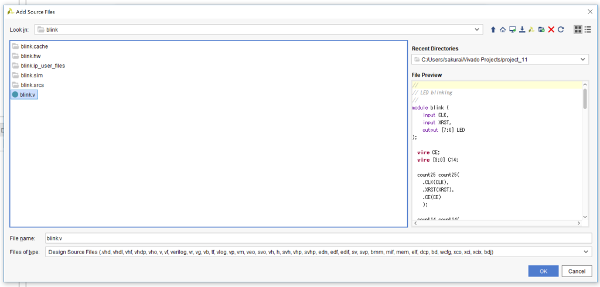

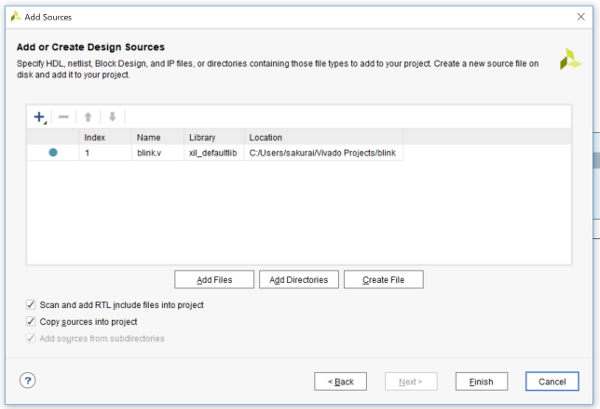

- blinkモジュール作成

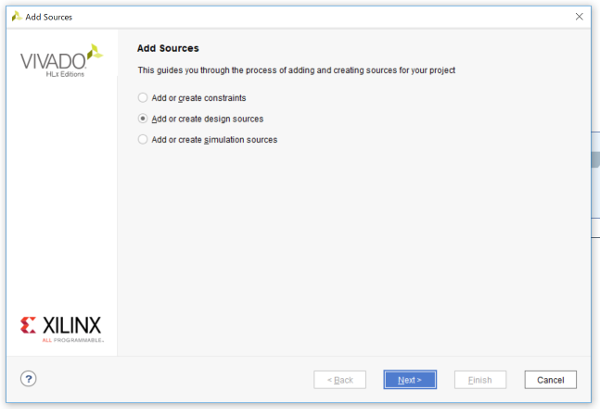

下図のように、Flow NavigatorのPROJECT MANAGERメニューからAdd Sourcesをクリックし、Add or create design sourcesラジオボタンを選択し、Nextをクリック。

- blinkモジュールをモジュールとして追加

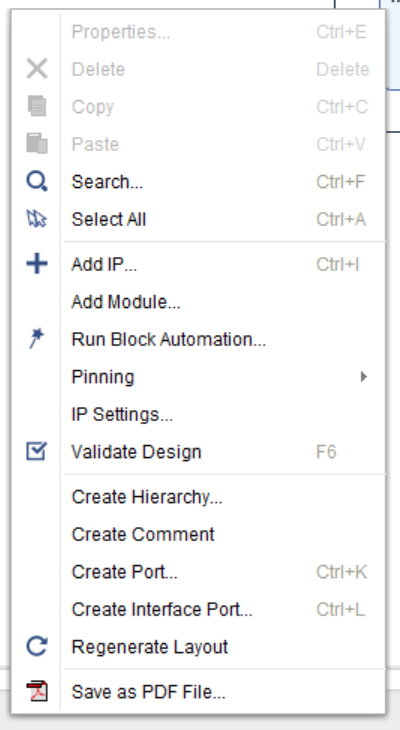

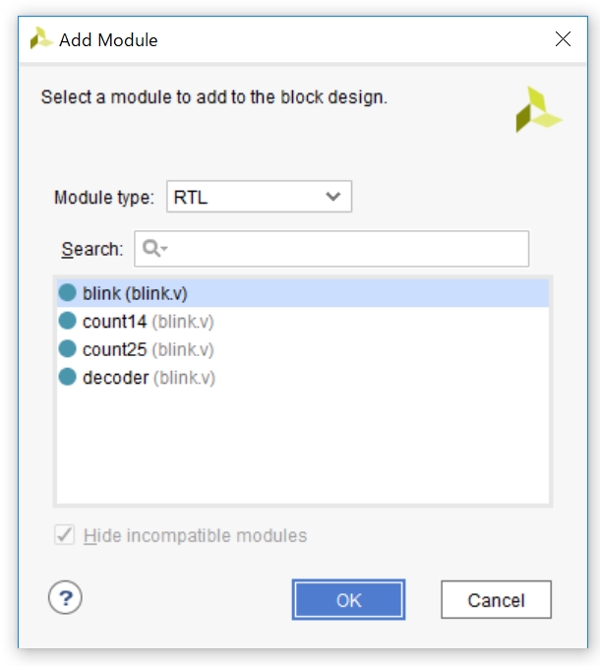

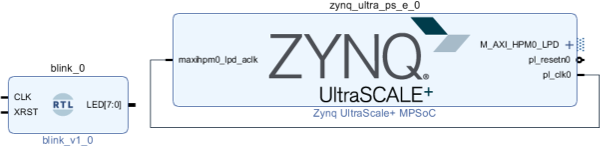

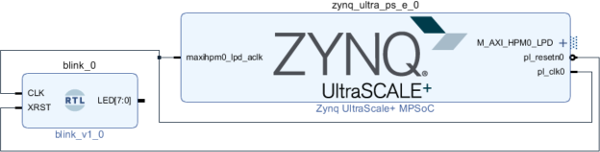

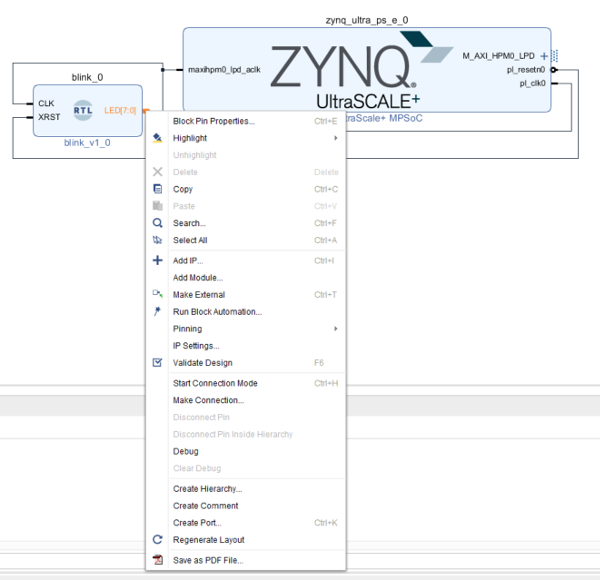

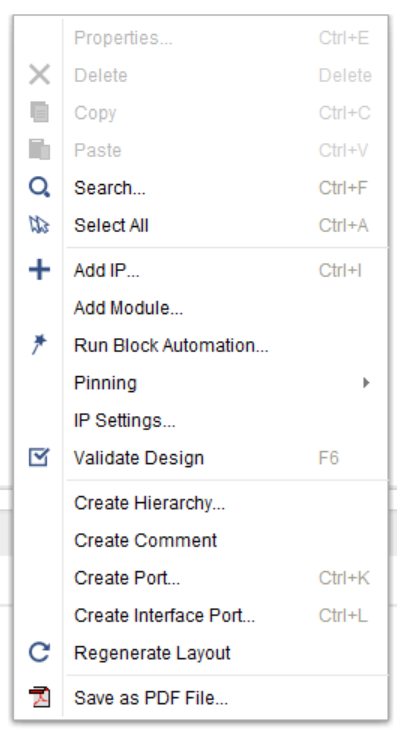

blinkモジュールが読み込めたので、blinkモジュールをブロック図にモジュールとして追加します。 何もないところで右クリックし、Add Moduleをクリック。