|

22 |

Pipeline processorの設計 (14) |

分岐命令

一般的な5段パイプラインを解説してきましたが、具体的なプロセッサを対象にして検討します。対象は何でも良いので、ここではRISC-Vとします。その理由は命令セットがオープンであり、誰でも自由に使用することができるためです。

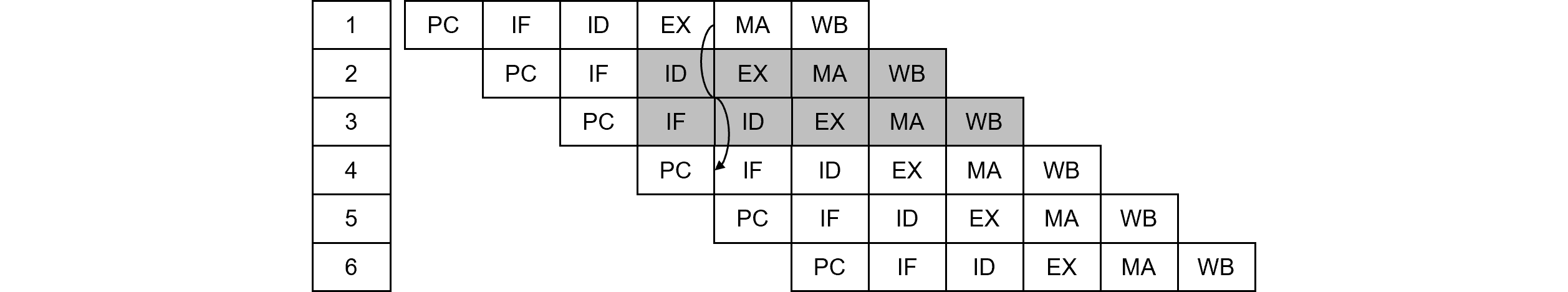

さて、前述の分岐命令は一般的にフラグを見て分岐判定を先行して行うRISCプロセッサでした。前の命令の<EX>で演算後にフラグを立て、その結果で次の分岐命令のデコードである<ID>終了時には分岐命令であり、かつ分岐条件が成立しているため、バブルは1$\tau$となります。

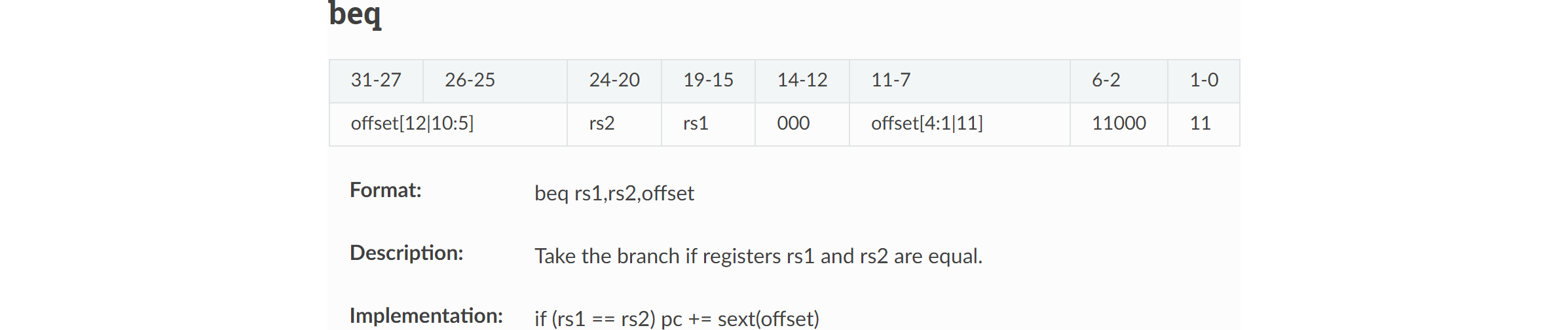

しかしながら、RISC-VのISAからの引用の図464.1を見ると、RISC-Vの条件分岐命令はレジスタをテストして、その結果で分岐するため、バブルは2$\tau$となります。そのため、前稿のフラグベースのアーキテクチャよりもこのアーキテクチャのほうが分岐レイテンシが長くなり、性能が悪いことになります。

それにもかかわらず、RISC-Vにおいて条件フラグを廃したのは、スーパスカラ化を考えると条件フラグの資源競合が起きやすくなるためだと思われます。

Leave a Comment