|

13 |

BSVによるメモリダンプモジュールの設計 (4) |

以下のスクリプトでVerilogシミュレーションを実行します。

$ bsc -verilog -u Tb.bsv

cp top-original.v top.v

emacs -nw top.v

// emacsでautomodeにより、top.vを生成

iverilog -y /usr/local/lib/Bluespec/Verilog/ top.v mkTb.v mkUart.v -o mkTb.exe

./mkTb.exe

gtkwave -A verilog.vcd

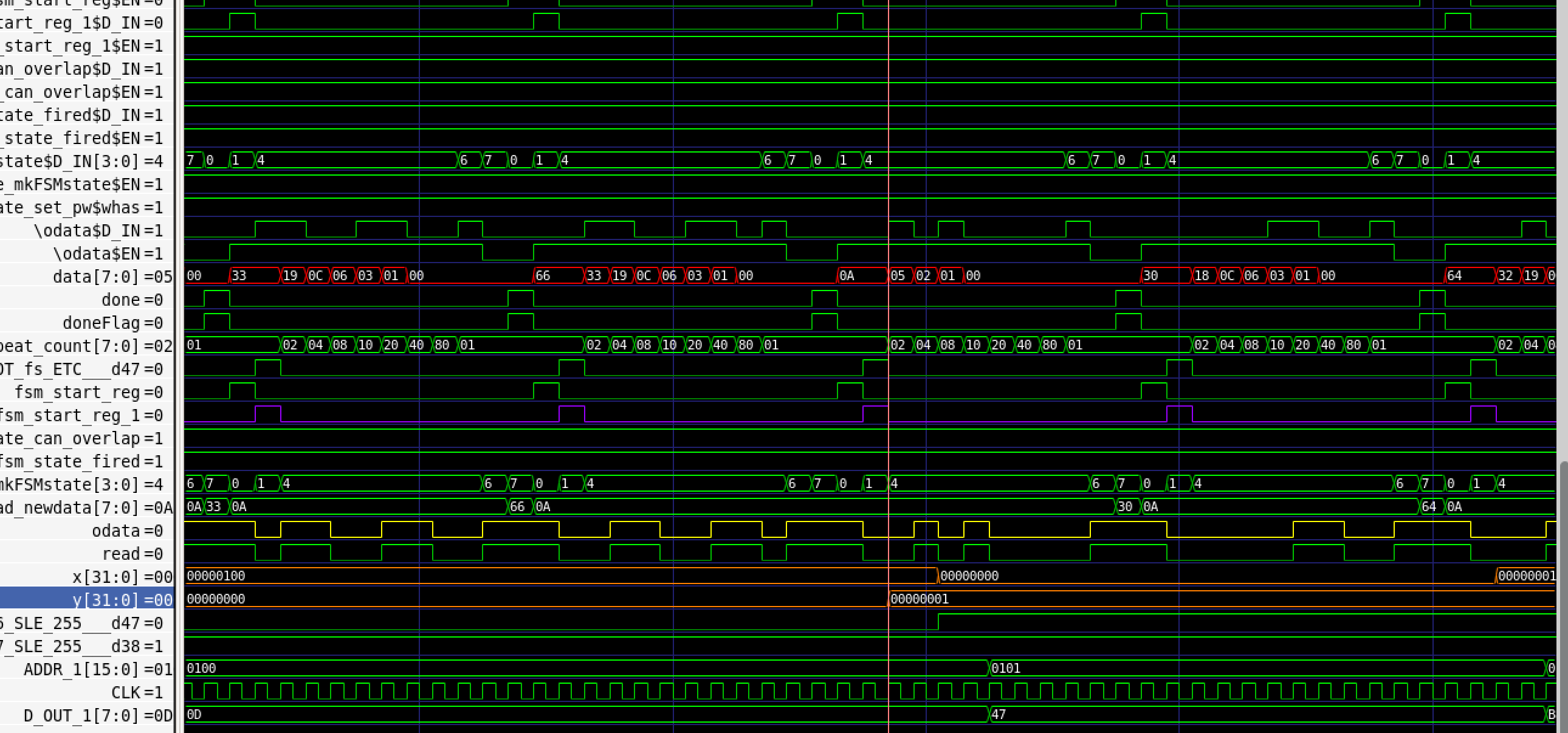

図はちょうど1行を送信したところで、横方向のxが256(xは255までだがチェックサム出力の際に256となる)から0に戻り、縦方向のyが0から1になった時点の波形です。データを0x33, 0x66, 0x0a, 0x30, 0x64と送信しています。

ストップビットを1ビットに削ったところ、1,582,090サイクルとなりました。1アスキーバイトあたり12サイクルなので、8bitの他、スタートが1bit、ストップが3bit相当となっています。送信時間は

- 115,200bpsでは6.9秒

- 230,400bpsでは3.4秒

- 460,800bpsでは1.7秒

- 921,600bpsでは0.9秒

となります。バイナリだとこれの半分の時間となるはずですが、デバッグの都合上アスキーコードの転送とします。

Leave a Comment