|

29 |

Lチカの実装 (4) |

Posts Issued in May, 2018

|

21 |

Lチカの実装 (3) |

RTL

以下にRTLを掲載します。元の要求を3分割し、アーキテクチャ設計として3つのエレメントの直列系により、目標となる要件を満足することができました。仕様を満たす動作をするかどうかはシミュレーションにより確認することができます。ただし、長いカウンタはシミュレーションを工夫しなければ、シミュレーション時間が非常に長時間になってしまいます。従って、任意の値をロードするようなテスト回路を挿入する工夫が必要となります。まずは基本の記述を掲載します。

Blinkモジュール

blinkモジュールは以下に示す、25bitカウンタ、14進カウンタ、LEDデコーダの3つのモジュールを含みます。

//

// LED blinking

//

module blink (

input CLK,

input XRST,

output [7:0] LED

);

wire CE;

wire [3:0] C14;

count25 count25(

.CLK(CLK),

.XRST(XRST),

.CE(CE)

);

count14 count14(

.CLK(CLK),

.XRST(XRST),

.CE(CE),

.C14(C14)

);

decoder decoder(

.C14(C14),

.LED(LED)

);

endmodule

25bitカウンタ

/* system clock division */

module count25 (

input CLK,

input XRST,

output CE

);

reg [24:0] count25;

always @(posedge CLK) begin

if (~XRST)

count25 <= 25'h0;

else

count25 <= count25 + 1'h1;

end

assign CE = (count25 == 25'h1ffffff);

endmodule

14進カウンタ

/* 14 advance counter for LED */

module count14 (

input CLK,

input XRST,

input CE,

output [3:0] C14

);

reg [3:0] count14;

always @(posedge CLK) begin

if (~XRST)

count14 <= 14'h0;

else if (CE)

if (count14 == 13)

count14 <= 0;

else

count14 <= count14 + 1'h1;

end

assign C14 = count14;

endmodule

LEDデコーダ

/* LED Decoder */

module decoder (

input [3:0] C14,

output reg [7:0] LED

);

always @* begin

case (C14)

0: LED = 8'b00000001;

1: LED = 8'b00000010;

2: LED = 8'b00000100;

3: LED = 8'b00001000;

4: LED = 8'b00010000;

5: LED = 8'b00100000;

6: LED = 8'b01000000;

7: LED = 8'b10000000;

8: LED = 8'b01000000;

9: LED = 8'b00100000;

10: LED = 8'b00010000;

11: LED = 8'b00001000;

12: LED = 8'b00000100;

13: LED = 8'b00000010;

endcase

end

endmodule

|

14 |

Lチカの実装 (2) |

RTL設計仕様

複雑な演算や制御を含む振る舞いは高位合成したくなりますが、このようなレベルであればRTLで十分でしょう。従ってVerilogで言うモジュールの要求を以下のようにブレークダウンします。これはLチカは要求であって実装可能な手段ではないため、実装可能な手段に分割することを意味します。

- 高速なクロックを分周し、目で見えるレベルの低速クロックとすること

- 低速クロックをカウントし、流れるパターンをひとつずつ表示すること

- 流れるパターンは14通りであるため、13を数えたら次は0とすること

- カウント値をデコードし、1つのLEDが点灯しているパターンとすること

1.の要求はNbitのカウンタで実装することができます。何ビットにするかは後程設計計算を行います。 2と3の要求は14進カウンタで実装することができます。一つの要求で一つのモジュールとは限りません。 4の要求はLEDデコーダとして実装することができます。以上でモジュール分割ができたことになります。

モジュール

名称: blink

インタフェース

次の表に、モジュール全体としてのインタフェース(入力及び出力)を示します。基本的にクロックとリセットが必要であり、後はどのLEDを点灯させるかを示す信号があるのみです。

| インタフェース信号名 | インタフェース信号内容 |

|---|---|

| CLK | 入力、100MHz |

| XRST | 入力、リセット信号、負論理を想定 |

| LED[7:0] | 出力、8bit、正論理、LEDへの出力信号 |

サブモジュール

(1) Nbitカウンタ

100MHzで点滅すると人間の目に見えないため、見える範囲にまでカウントします。最後の桁上げの際に次段のカウンタを1だけ増加させます。これにより元のクロックが$2^N$分周されることになります。

0からアップカウントし、Nbitの全てのビットが1になった場合に次段のカウンタイネーブルをtrueとします。

前記のように人間の目で見える範囲内に入れるためには、例えば周期を0.5secから1.0sec未満の範囲として以下の不等式を解くことになります。 \[ 0.5\le \frac{2^N}{1e8} \lt 1.0 \] この不等式が成立する整数解Nはただ一つであることが保証され、これを解くとN=25[bit]となります。これは非機能要求である性能要求による設計計算を実施し、仕様が決定したことになります。

(2)14進カウンタ

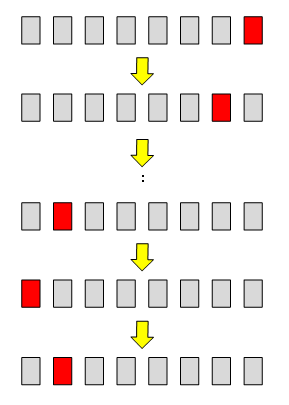

最右のLEDが点灯しているパターンから左にシフトし、さらに右に戻ってくるまでのパターンが以下の表に示すように14パターンあるため、14進カウンタを設けます。14進カウンタのイネーブルは前記Nbitカウンタからのカウンタイネーブルを接続します。

| カウント値 | パターン |

|---|---|

| 0 | 8'b00000001 |

| 1 | 8'b00000010 |

| 2 | 8'b00000100 |

| 3 | 8'b00001000 |

| 4 | 8'b00010000 |

| 5 | 8'b00100000 |

| 6 | 8'b01000000 |

| 7 | 8'b10000000 |

| 8 | 8'b01000000 |

| 9 | 8'b00100000 |

| 10 | 8'b00010000 |

| 11 | 8'b00001000 |

| 12 | 8'b00000100 |

| 13 | 8'b00000010 |

(3)デコーダ

14進カウンタの出力はバイナリ出力のため、表41.2のビットパターンとなるようにデコーダを設けます。

今回の設計ではアップカウンタのみで構成しましたが、デコーダを倹約してアップダウンカウンタで構成することも可能です。結局のところ、設計とは新しいことを生み出すというよりも、実装できるレベルの小規模のサイズに分割し、そのトレードオフを最適化することにほかなりません。

|

7 |

Lチカの実装 |

要求

「Lチカを実現すること」

いわゆるLチカとは評価ボード上のLEDが点滅することで、回路が思い通りに動作していることを示す振る舞いの一例です。LEDの点滅は機能要求ですが、暗黙の非機能要求があります。例えば点滅の周期です。評価ボードは内部クロックは100MHzという高速のクロックで動作しますから、単純にON/OFFさせると人間の目には点滅に見えません。従って点滅と書かれている段階で点滅に見えることが暗黙の非機能要求であり、例えば、点灯を0.5sec、消灯を0.5secのように連続させる必要があります。

PLに接続されているLEDは8bitあるので、右から左に1bitずつずらしながら点灯し、最左端に来たら左から右へ1bitずつ点灯することを要件とします。下図において、赤は点灯、灰色は消灯を意味するものとします。