|

6 |

RISC-Vプロセッサの設計 (28) |

前回まではパイプラインのうち<IF>にwaitを入力しましたが、基本的に<WB>以外のステージにwaitが入る可能性があります。

| ステージ | ウエイト信号 | ウエイト原因 | パイプライン処理 |

|---|---|---|---|

| <PC> | pc_wait | PCの到着が遅れる場合。例えば分岐キャッシュから出力されるPCが遅れる場合。 | 上流へは同一サイクルでの停止とし、下流へはパイプラインバブルを流す。 |

| <IF> | if_wait | 命令メモリから出力される命令データの到着が遅れる場合。例えばIキャッシュミスによるブロックインの場合。仮想記憶サポートの場合は、I-TLBミスによるページテーブルウォーク。 | 上流へは同一サイクルでの停止とし、下流へはパイプラインバブルを流す。 |

| <ID> | mc_wait | 命令デコーダは1サイクル内で実行できるため、後続を待たせる必要が無いのでid_waitは無し。マルチサイクル命令の場合は内部的にパイプラインストリームを生成する処理。 | 上流へは同一サイクルでの停止とし、下流へはvalidな命令を内部的に複数生成し、パイプラインで流す。マルチサイクル(かつ複数パイプラインストリーム)動作なのでパイプラインバブルは流さない。 |

| <EX> | ex_wait | 演算器から出力されるデータの到着が遅れる場合。複数サイクル演算が必要な例えば4サイクル乗算器のような演算。 | 上流へは同一サイクルでの停止とし、下流へはパイプラインバブルを流す。 |

| <MA> | ma_wait | データメモリから出力されるデータデータの到着が遅れる場合。例えばDキャッシュミスによるブロックインの場合。仮想記憶サポートの場合は、D-TLBミスによるページテーブルウォーク。 | 上流へは同一サイクルでの停止とし、下流へはパイプラインバブルを流す。 |

| <WB> | --- | WBは1サイクル内で実行でき、後続が無いのでwb_waitは無し。 | --- |

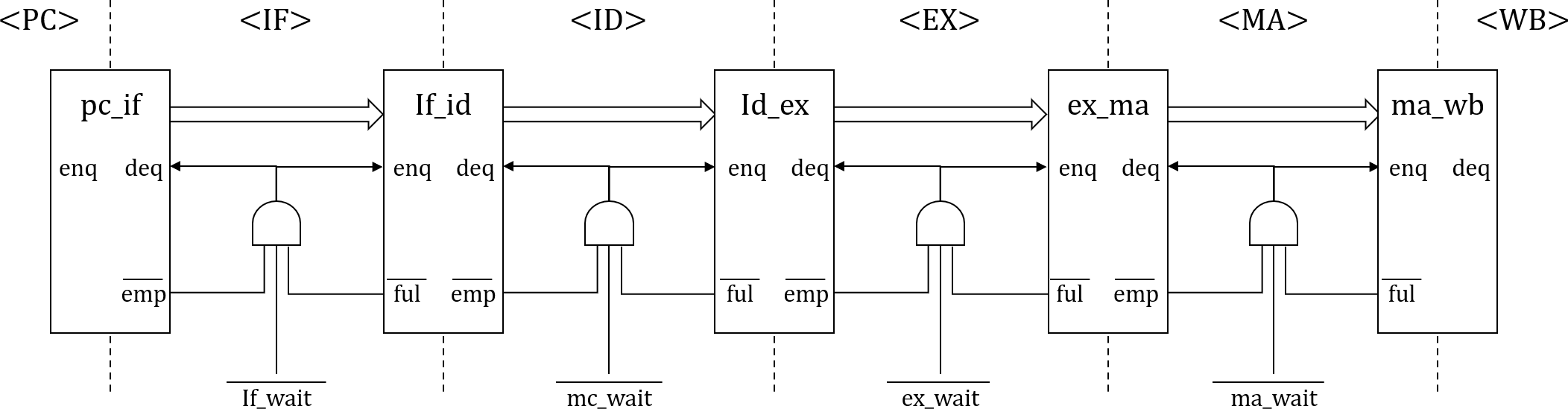

図673.1に各種wait信号を入力したデータパイプライン構造を示します。過去記事で調べた回路にwaitが追加されています。

図では信号名を3文字に短縮していますが、$\overline{\text{emp}}$は$\overline{\text{empty}}$の略でdeqのenable信号、$\overline{\text{ful}}$は$\overline{\text{full}}$の略で、enqのenable信号です。

Leave a Comment