|

21 |

Cmod A7の利用 (6) |

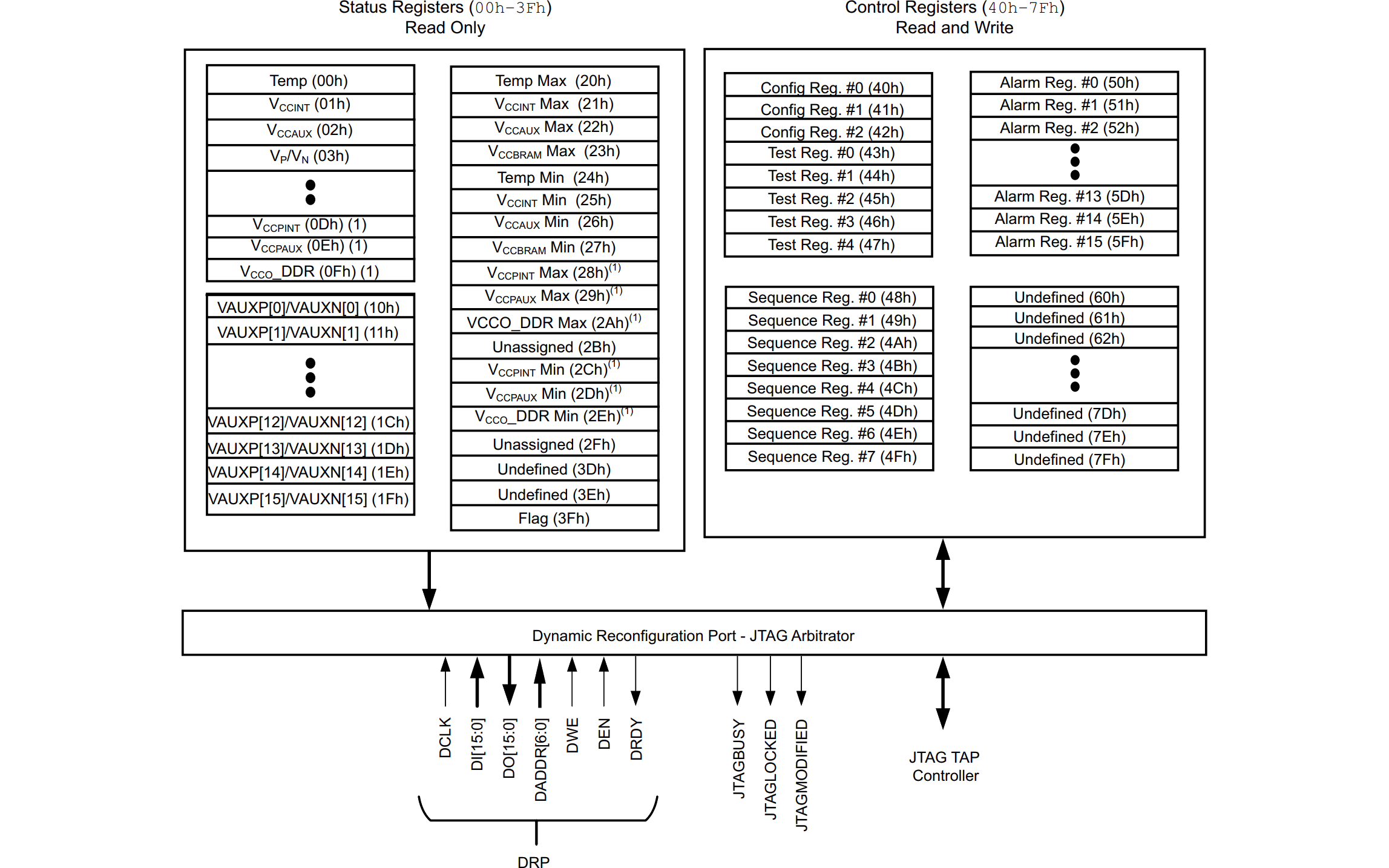

DRPからアクセス可能な各種ステータスレジスタ及びコントロールレジスタを示します。

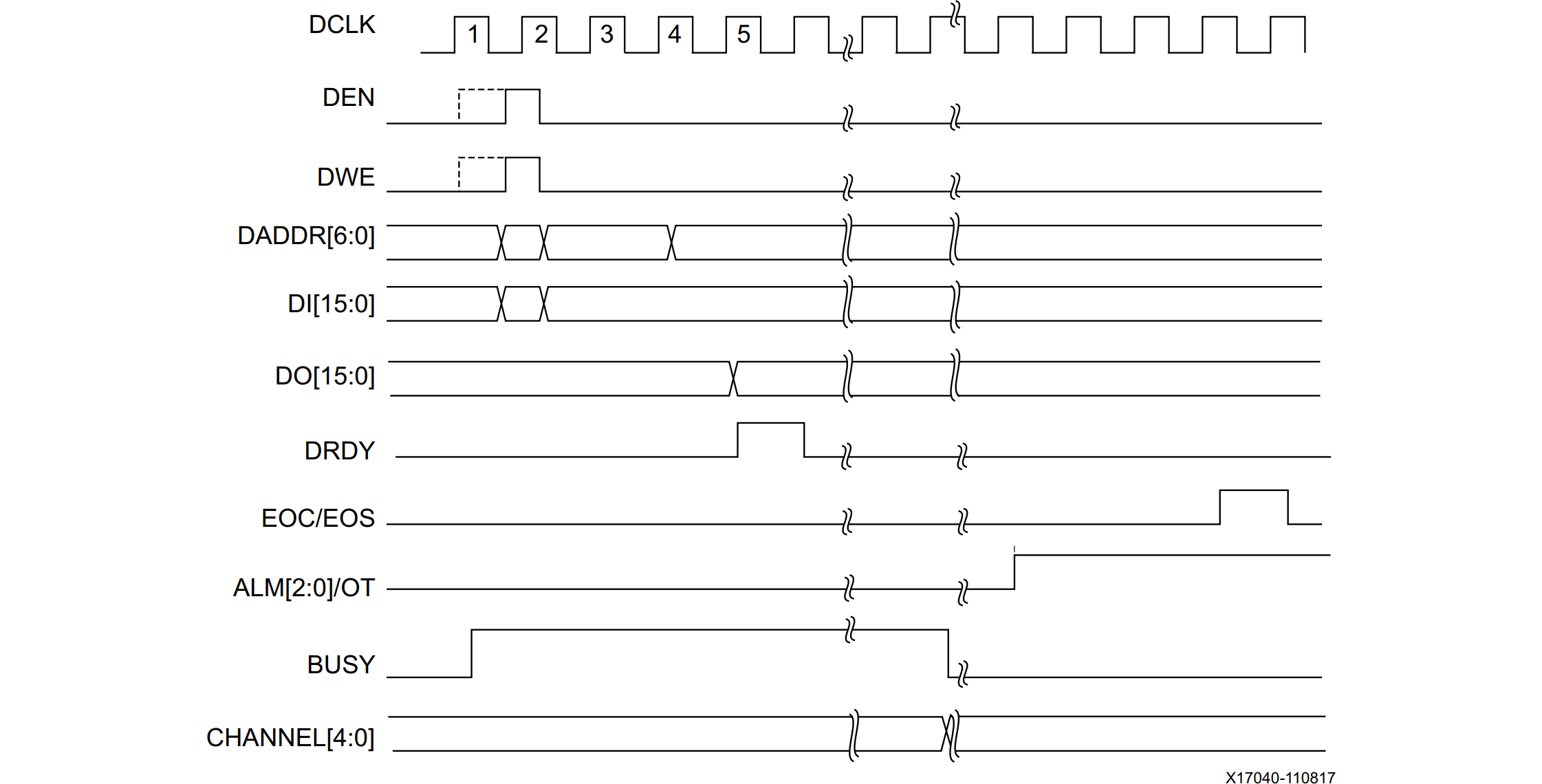

次にDRPアクセスタイミングを示します。

この仕様に従ってADCデータを読み出すFSMをBSVでプログラミングします。BSVではStmtFSMライブラリを用いることによりシーケンシャルな処理を実行するFSMが容易にかけるため、FSMの設計に何ら痛痒を感じません。ただし結果としてはEOC(End of conversion)をDEN(DRP Enable)に接続し、Continuousモードに設定するだけで連続的にADC値が出力されるため、シーケンサを組む必要はありませんでした。

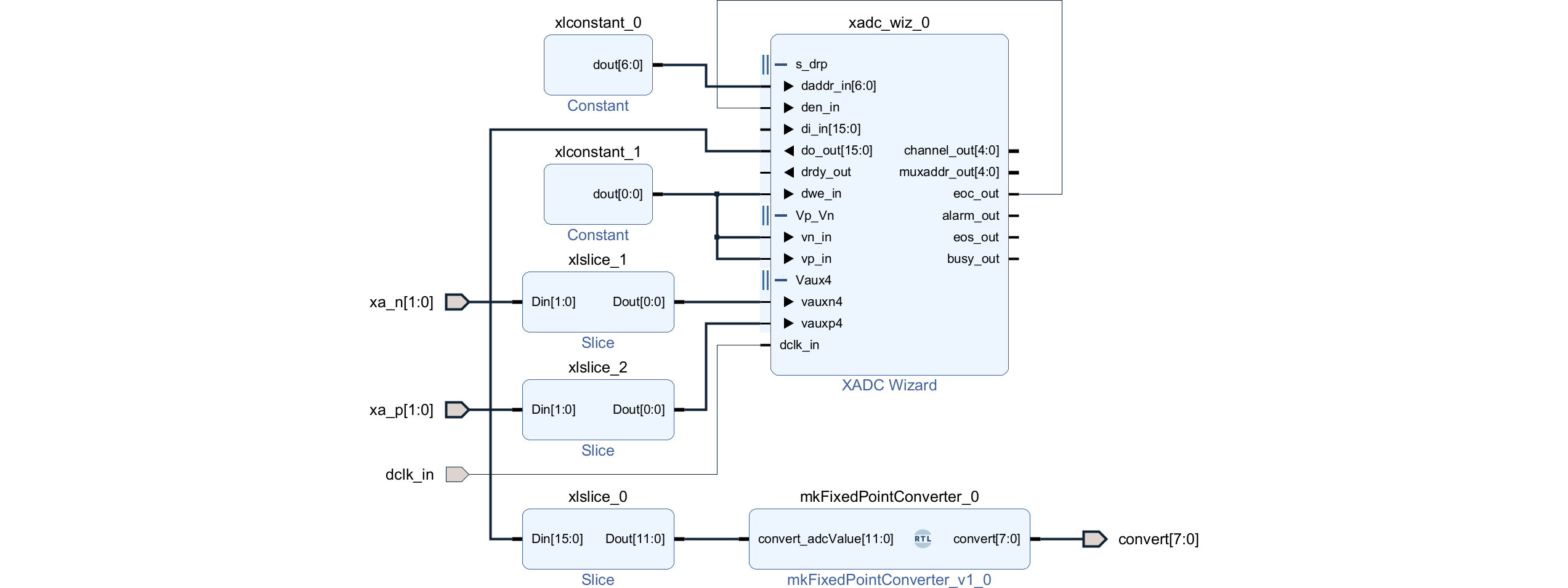

完成したADCソフトブロックを以下に示します。ADCの出力に接続しているのは、ADC値からy座標に変換する回路(#705で設計予定)です。

Leave a Comment