|

5 |

6809の改造 - HALT端子の追加 |

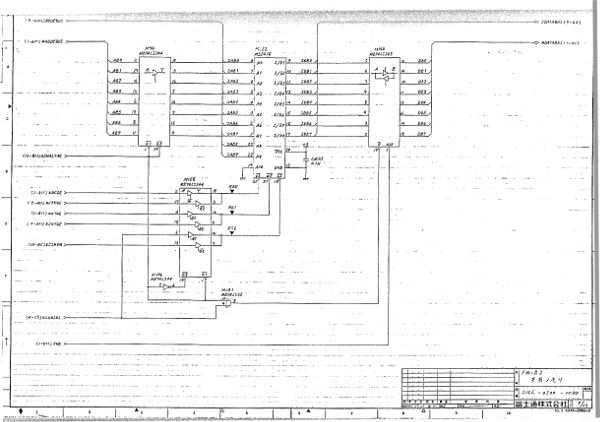

さて、サブシステムの共有メモリを実装する際には、実機では図141.1のようにメインCPUがサブCPUをHALTさせてアクセスしています。前稿のように、共有メモリは128ByteとなっていてメインCPUとサブCPUの間に物理的な128Byteのメモリがあるように思えますが、実態はサブCPUの物理メモリ(MB8416, 2KB SRAM)の半分しか使用しておらず(\$D000~\$D3FFの1KB SRAMとして使用)、さらにそのうちのメインCPUから見える窓が128Byteであり、メインCPUが使用する際にはHALTをかけてサブCPUのバスを開放し、メインCPUがアクセスするという構造のようです。

物理メモリのMB8416がシングルポートで同時にアクセス不可であるため、HALTによりバスを開放させています。FPGA実装では、デュアルポートRAMが可能なので同時アクセス可なのですが、同時にアクセスすると、サブCPUがコマンドを読み出し中に、メインCPUが書き換えてしまうという論理的なデータ競合の問題が起こります。従って、メインCPUとサブCPUの論理的な同期化のために、HALT信号が必要です。

ところが、図138.2をみてもわかるように、本IPの信号はLSIの6809と異り、HALT端子がありません。従って、HALTREQ、HALTACK端子を実装します。

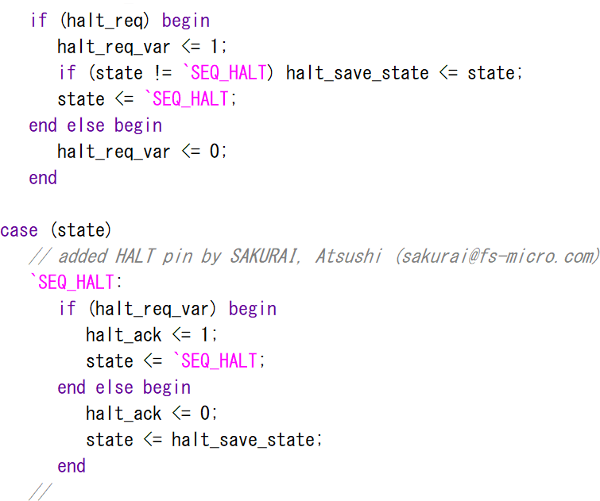

IPの6809のソースを追うと、FSMの最初に割込み受信のコードが存在します。その辺に以下のような疑似コードを挿入します。HALTREQ信号をhaltreq変数に入れているのは、HALTREQ信号を見るのは一か所にしたかったためです。逆に複数個所でHALTREQ信号を見ると、状態の不一致が起きる可能性があります。

もしHALTREQ信号がHならば、

haltreq変数をHにし、

現stateがSEQ_HALTで無い場合にのみ、stateを戻りステートとして保存し、

次のサイクルでSEQ_HALTに移行

そうでなければ

haltreq変数をLにする

SEQ_HALT:

もしhaltreq変数がHならば、

HALTACKをHにし、

次のサイクルでSEQ_HALTに移行

そうでなければ、

HALTACKをLにし、

次のサイクルで戻りステートに移行

これをVerilogで記述すれば、

となります。

Leave a Comment