|

28 |

BSVにおけるコマンドバッファ制御 (9) |

6. Verilogシミュレーション

次にverilogシミュレーションを実行します。

$ make vsim

bsc -verilog -bdir vobj -u -g mkTopDirect -vdir rtl TopDirect.bsv

checking package dependencies

All packages are up to date.

bsc -verilog -bdir vobj -vsearch rtl -e mkTopDirect -o mkTopDirect.vexe

Verilog binary file created: mkTopDirect.vexe

./mkTopDirect.vexe +bscvcd=vsim.vcd +bscdumpvars

VCD info: dumpfile vsim.vcd opened for output.

5: produce = 1

5: consume = 1

205: produce = d

205: consume = d

405: produce = e

405: consume = e

605: produce = a

605: consume = a

805: produce = b

805: consume = b

1005: produce = 6

1005: consume = 6

1205: produce = 8

1205: consume = 8

1405: produce = 2

1405: consume = 2

1605: produce = 9

1605: consume = 9

1805: produce = f

1805: consume = f

=== simulation finished ===

rtl/mkTopDirect.v:115: $finish(1) called at 1815 (1s)

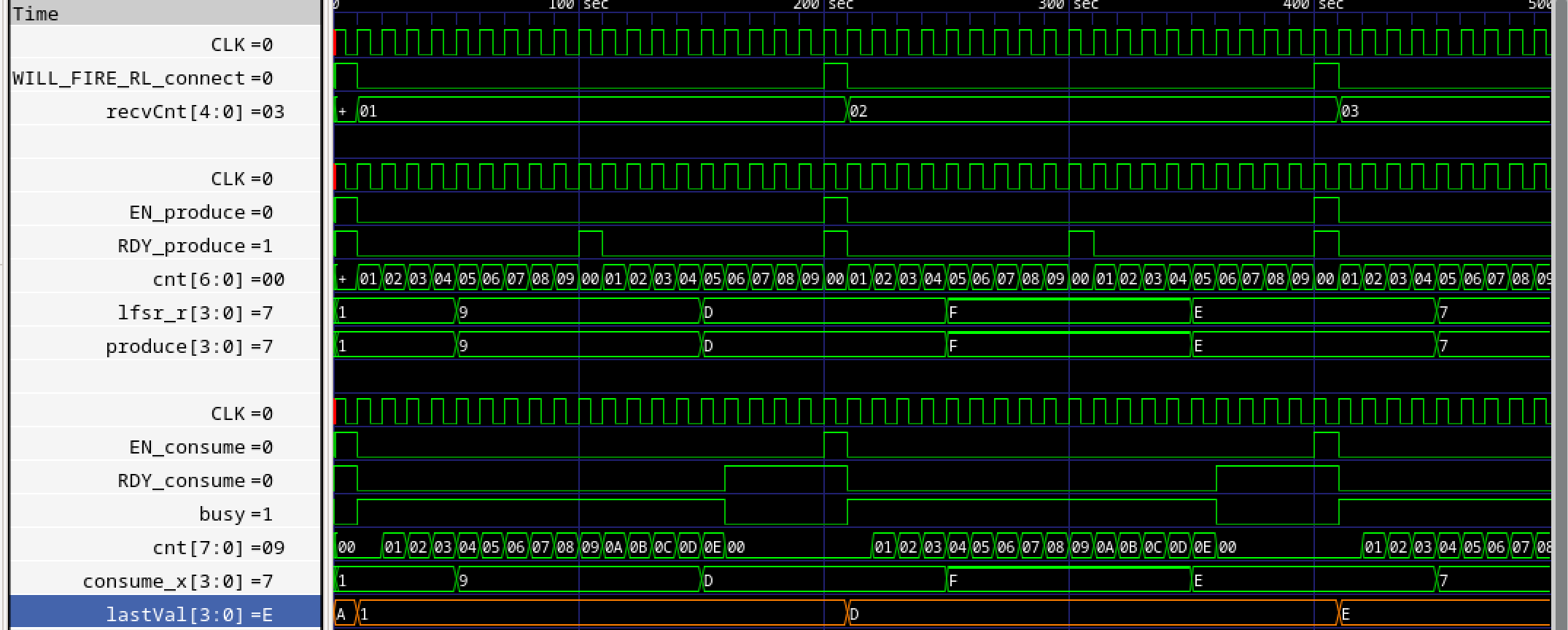

シミュレーション波形を確認します。

$ gtkwave -A vsim.vcd

verilogシミュレーションではモジュール階層は保たれており、producerが適当なタイミングで値を変更しますが、consumerは自分のタイミングでそれを受け取ります。両方のタイミングが揃った時がtopで見えているWILL_FIRE_RL_connectです。従って、1$\rightarrow$9$\rightarrow$D$\rightarrow$F$\rightarrow$EというProducerの動作に対して9, Fの取りこぼしが起きているのが確認できます。

この取りこぼしの原因は上流のスループット1/10よりも下流のスループット1/15が低い、かつバックプレッシャーをかけてないために、上流から見て3回に1回は取りこぼすことになります。

Leave a Comment