|

17 |

Cmod A7の利用 (5) |

Artix 7シリーズFPGAのADCを利用するには、ただ読み込めば良い基板上のスイッチと異なりいろいろと制約があるようです。ADCのユーザーズガイド(UG480)に書かれていますが、DRP(Dynamic Reconfigure Register)経由で読み出すとのことです。

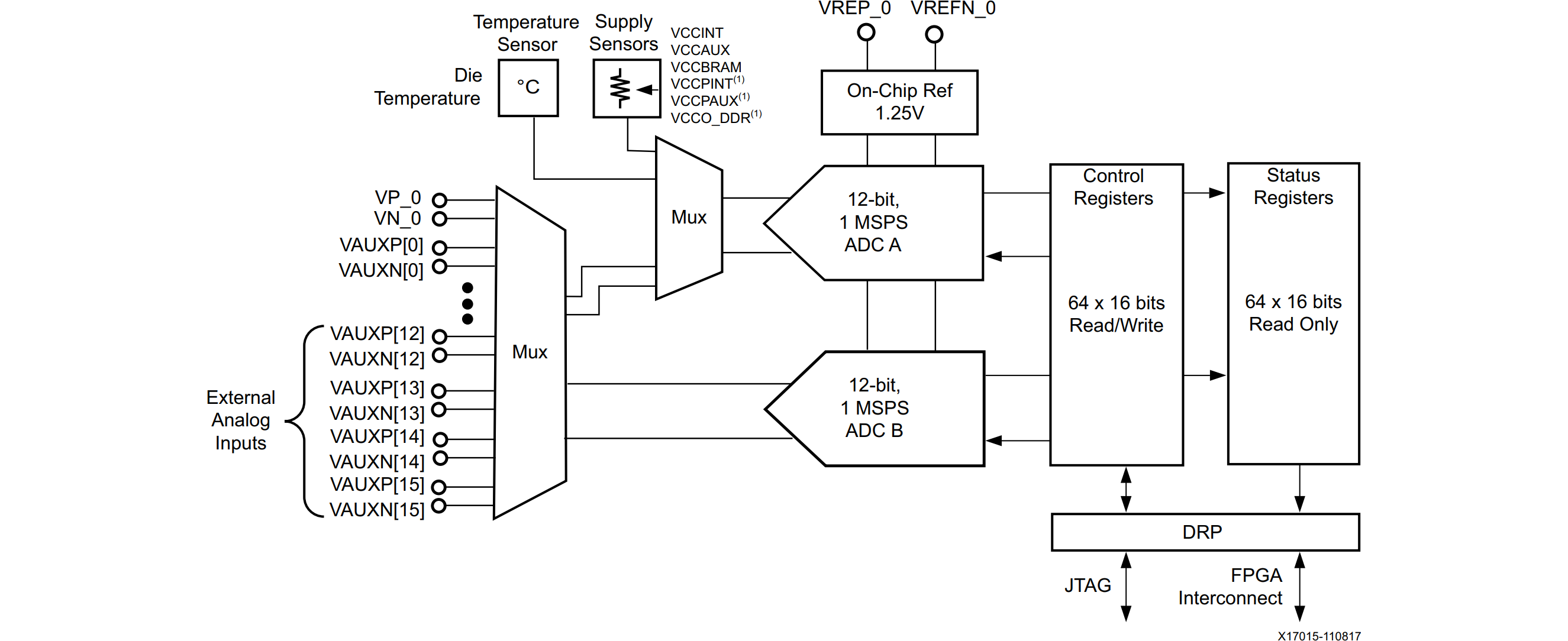

その日本語版 (UG480) のXADCの概要によれば、

XADC には、オンチップ電源電圧とダイ温度の測定をサポートするいくつかのオンチップ センサーも含まれています。ADC 変換データはステータス レジスタと呼ばれる専用レジスタに格納されます。これらのレジスタは、ダイナミック リコンフィギュレーション ポート (DRP) と呼ばれる 16 ビットの同期読み取り/書き込みポートを使用して、FPGA インターコネクト経由でアクセスできます。

とのことであり、以下にブロック図を示します。右下にDRPブロックがあります。

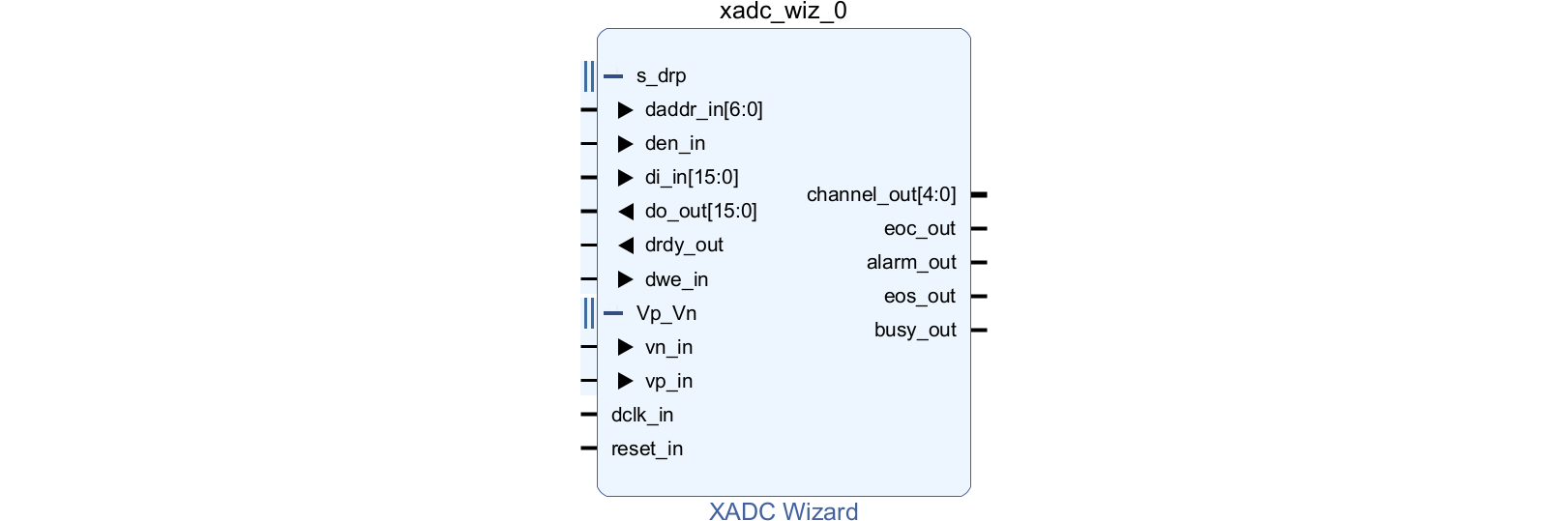

VivadoにおいてはXADC Wizardによりパラメータを設定してからインスタンスします。

- Vivadoのブロックデザインエディタにおいて、右クリックからAdd IPをクリック、XADC Wizを開く。

- Basicタブにおいて、Interface OptionをDRPとする。

- Timing ModeはContinuous Mode

- startup Channel SelectionはSingle Channel

- DRP Timing Optionは無設定(DCLKは100MHzがデフォルト)

- AXI4Sは無設定

- Control/Status Portsは無設定

- ADC Setupタブにおいて、全てを無設定、None、空欄とする。

- Alarmsタブにおいても同様。

- Single ChannelタブはChannel Enableにチェック

以上を設定のうえOKをクリックすると図のようなモジュールが生成されます。WizardではXADCが内部にインスタンスされたラッパーモジュールを生成します。