|

20 |

FPGAで機械学習 (2) |

|

資料やデータの入手

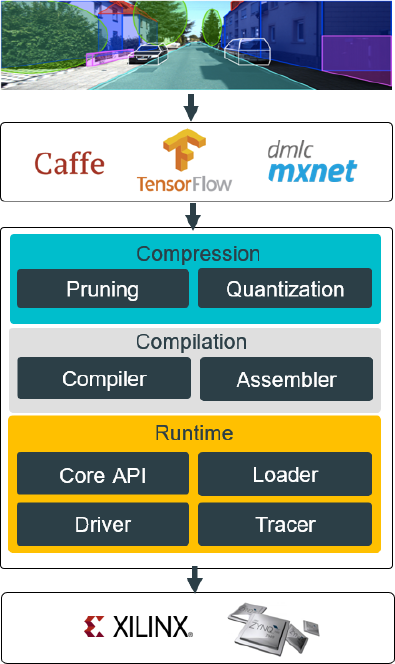

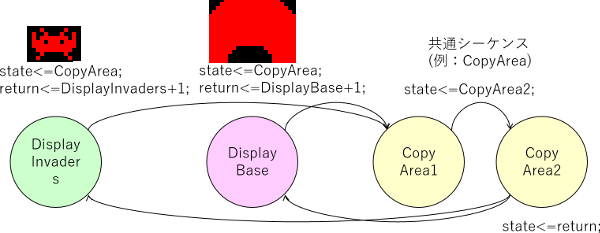

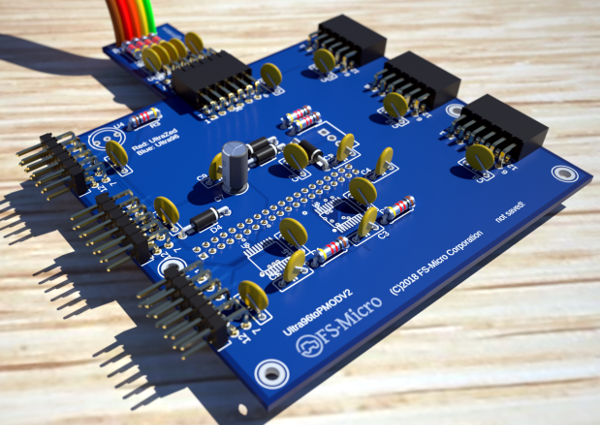

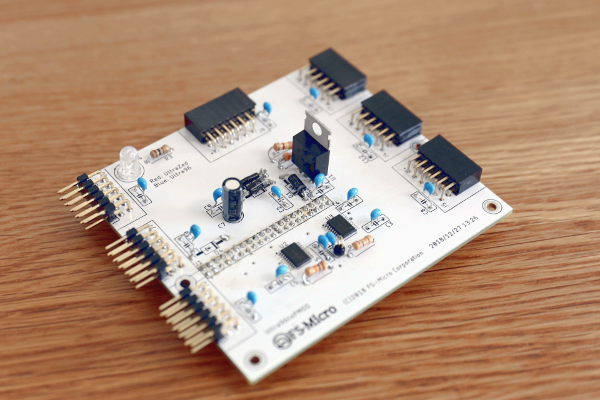

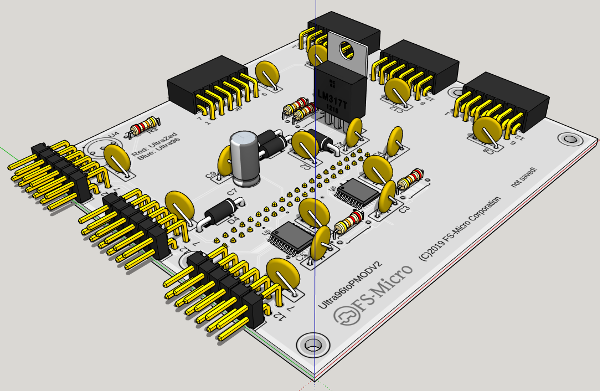

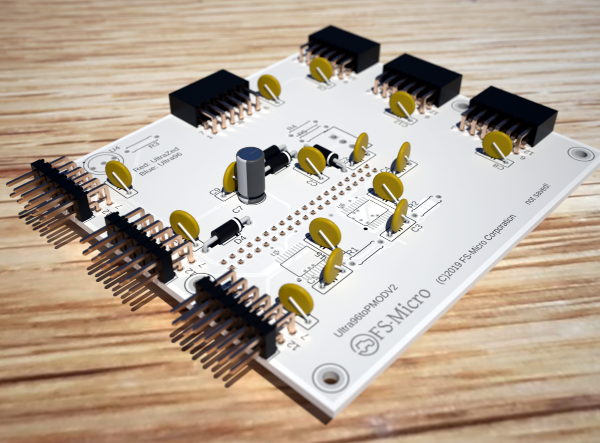

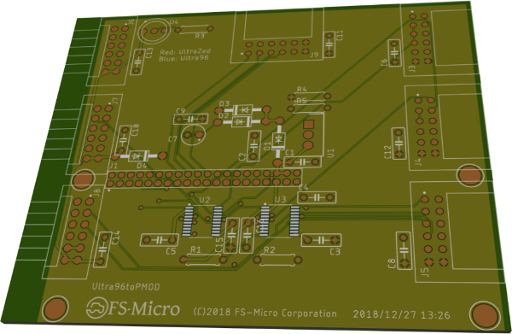

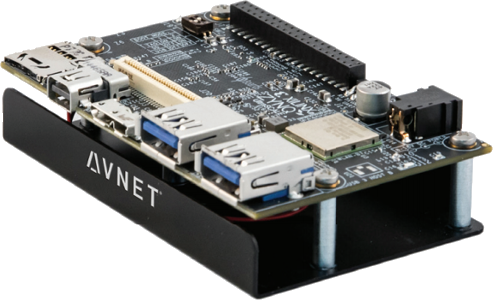

まずXilinxのアカウントは所持しているものとします。次にXilinxのエッジAI開発者ハブのページに行き、以下に示すデータをダウンロードします。ここで対象の評価ボードは、過去記事でインベーダーゲームを搭載したUltra96ボードを使用します。

- ユーザーズガイド --- DNNDK ユーザー ガイド (UG1327)

- デモプログラム --- xlnx_dnndk_2.08_1901.tar.gz

- 評価ボードイメージ --- xilinx-ultra96-desktop-stretch-2018-12-10.img.zip

SDカードへブートイメージの焼きこみ

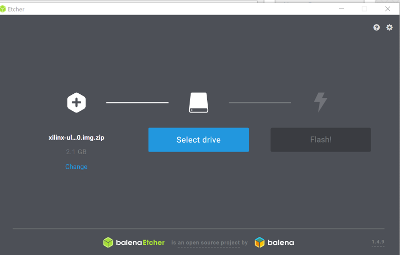

基本的には上記ユーザーズガイドに基づいて実施します。まずSD焼きソフトであるEtcherを入手します。次に上記評価ボードのブートイメージファイルを、zipは解凍しなくても大丈夫なので、そのままEtcherでSDに焼きます。

デモプログラム類の書き込み

デモプログラムやデータを評価ボードに移さなければなりません。ユーザーズガイドではネットワークでscpすると記述されていますが、Ultra96の無線LANがうまくつながらなかったため、SDにあらかじめ移しておくことにしました。

VirtualBox等のVMを用いたLinuxでSDをマウントしてコピーします。USBインタフェースを持つSDカードリーダを使用しました。VMにおいてはUSBをVM側で見えるように設定しておく必要があります。

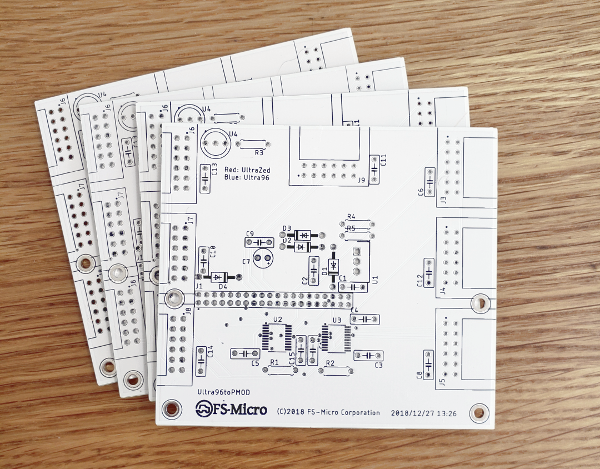

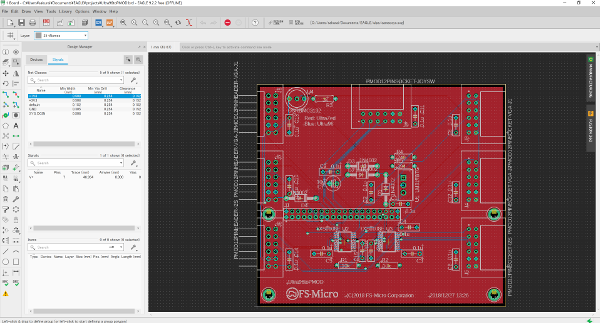

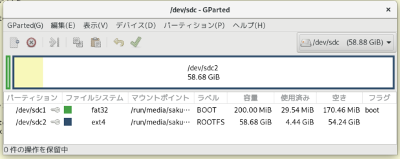

上記イメージを書き込んだSDは、図88.2のように第1パーティションがFAT32、第2パーティションがext4となっています。第2パーティションをGpartedで拡張しておきます。

デモプログラムは800MB以上あるため第1パーティションには入らないので、第2パーティションにコピーします。

virtaul_machine # cp xlnx_dnndk_2.08_1901.tar.gz /run/media/user/ROOTFS/home/linaro/

virtual_machine # sync