|

21 |

RISC-Vプロセッサの設計 (22) |

2段FIFOの修正

前記事で記載したようなウエイト制御を行えば、実質的に2段FIFOのd1は使用することはないはずです。従ってFIFO2.vからd1の本体及び関連制御信号を削除してしまいます。これによりウエイトシミュレーションを実施しましたが、結果は同様でした。これで実質FIFO1を設計することができました。

違いは、元のFIFO1ではempty=!fullというロジックだったものが、新FIFO1ではemptyとfullが3状態を取るようになったことです。しかし、1段しか無いということは永久にfullにはならないということなので、元のFIFO1でfullをFalse固定としても動作しそうです。

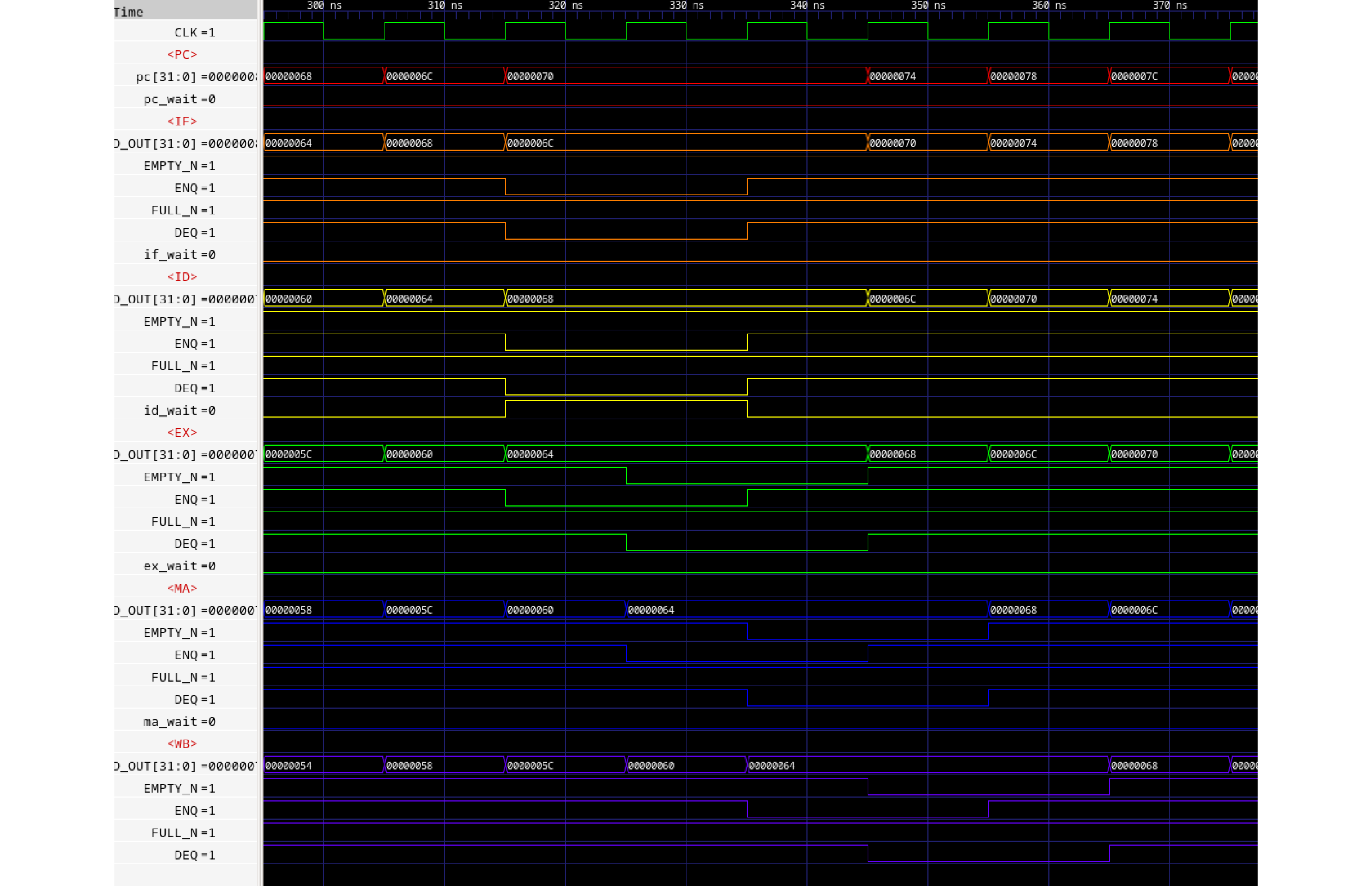

早速元のFIFO1を修正してシミュレーションしてみました。

同じく、読み取りにくいので表にしてみます。

| ステージ | 0 | 1 | 2 | 3 | 4 | 5 | 6 |

|---|---|---|---|---|---|---|---|

| PC | 006c | 0070 | 0070 | 0070 | 0074 | 0078 | 007c |

| IF | 0068 | 006c | 006c | 006c | 0070 | 0074 | 0078 |

| ID | 0064 | 0068 | 0068 | 0068 | 006c | 0070 | 0074 |

| EX | 0060 | 0064 | 0064 | 0064 | 0068 | 006c | 0070 |

| MA | 005c | 0060 | 0064 | 0064 | 0064 | 0068 | 006c |

| WB | 0058 | 005c | 0060 | 0064 | 0064 | 0064 | 0068 |

オリジナルFIFO2と全く同じ結果となりました。

Leave a Comment