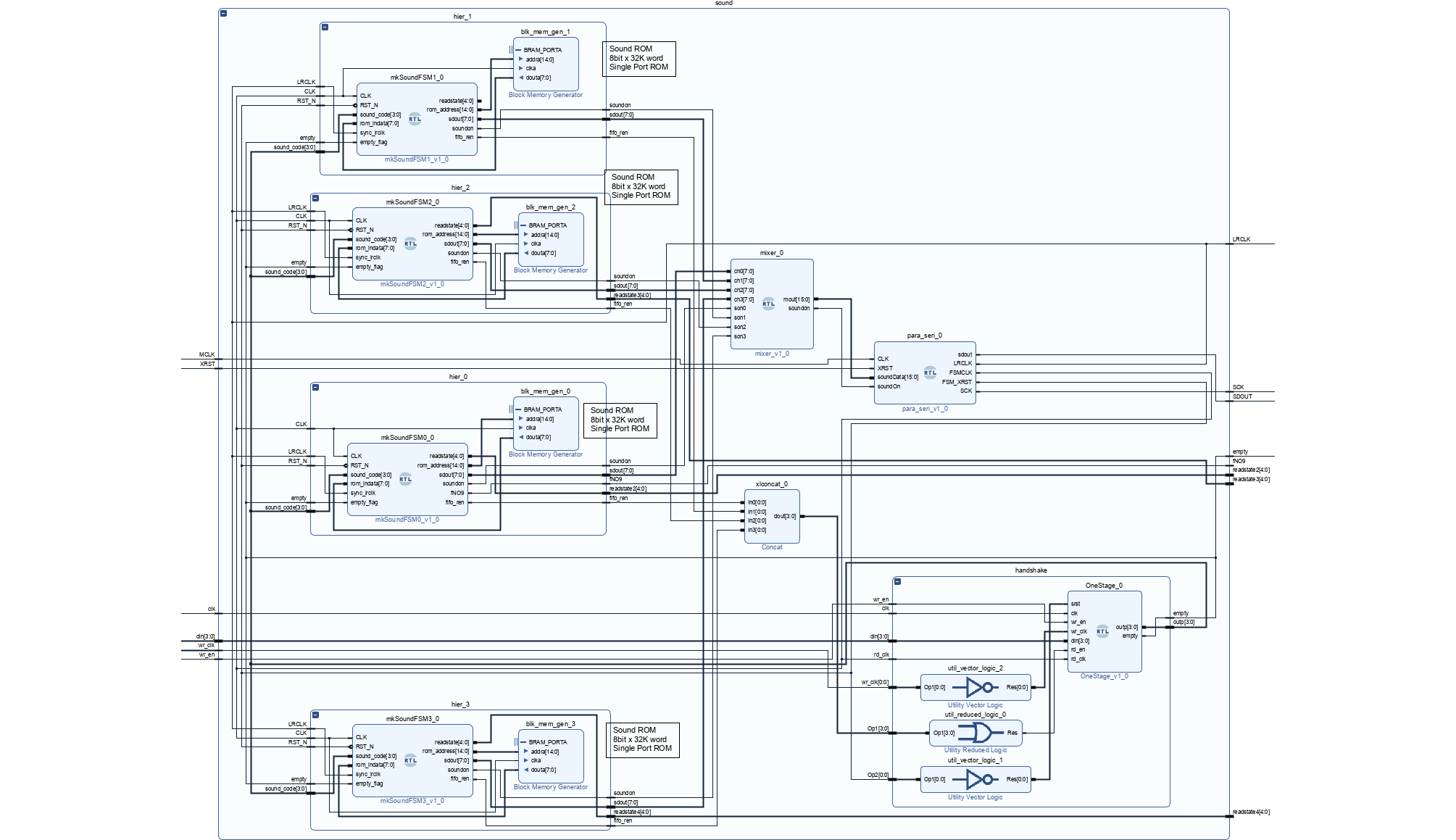

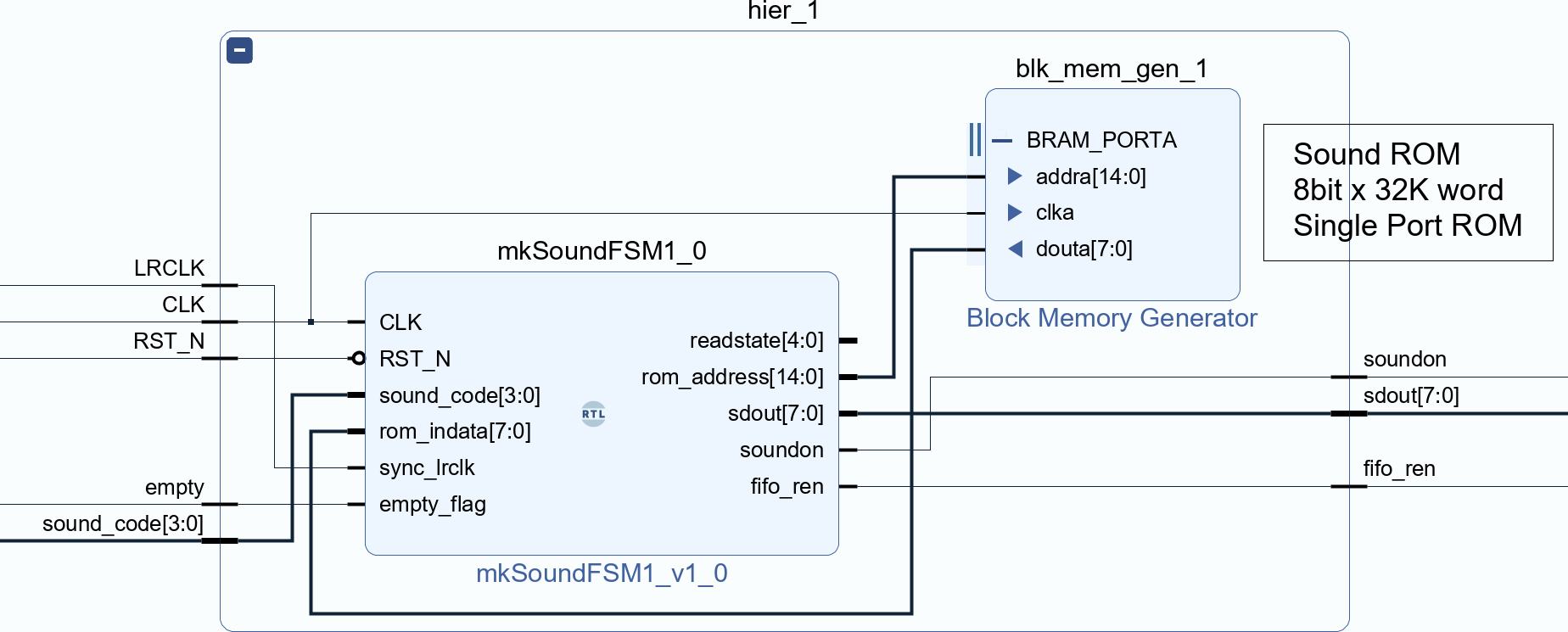

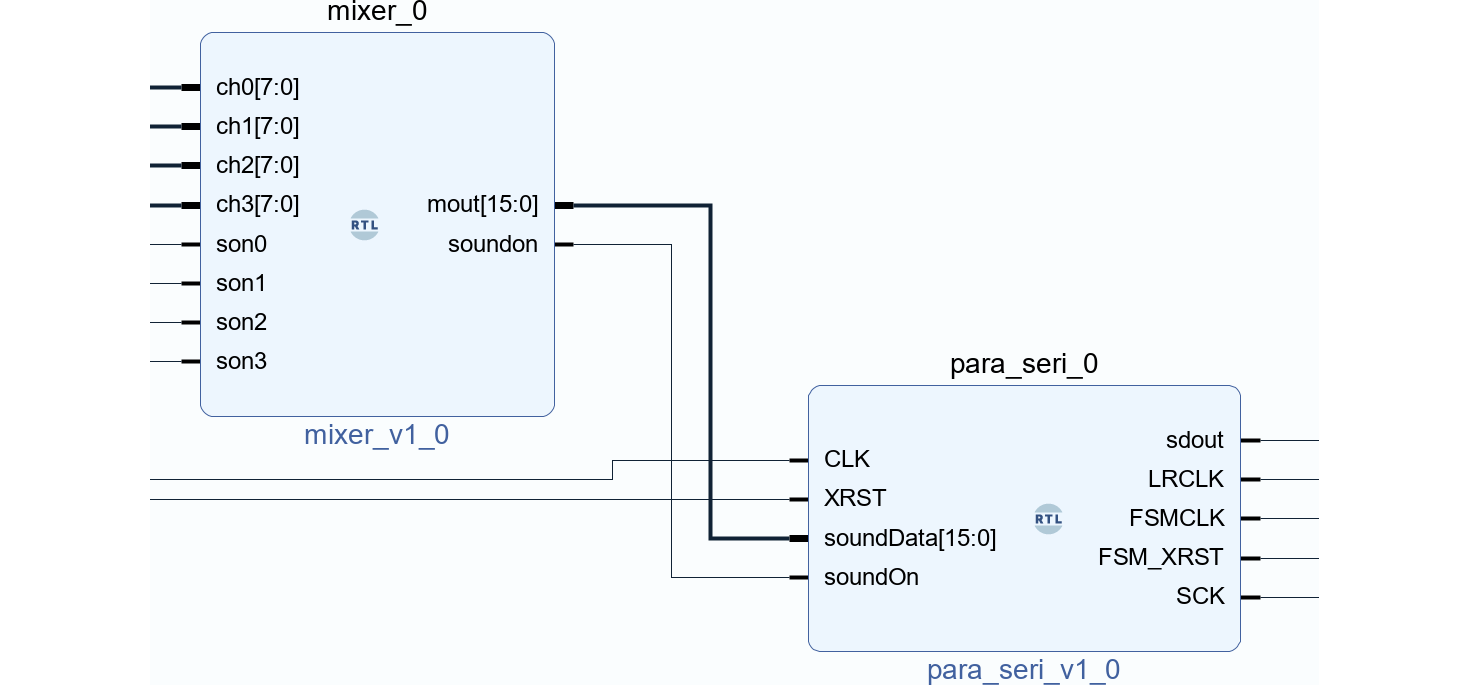

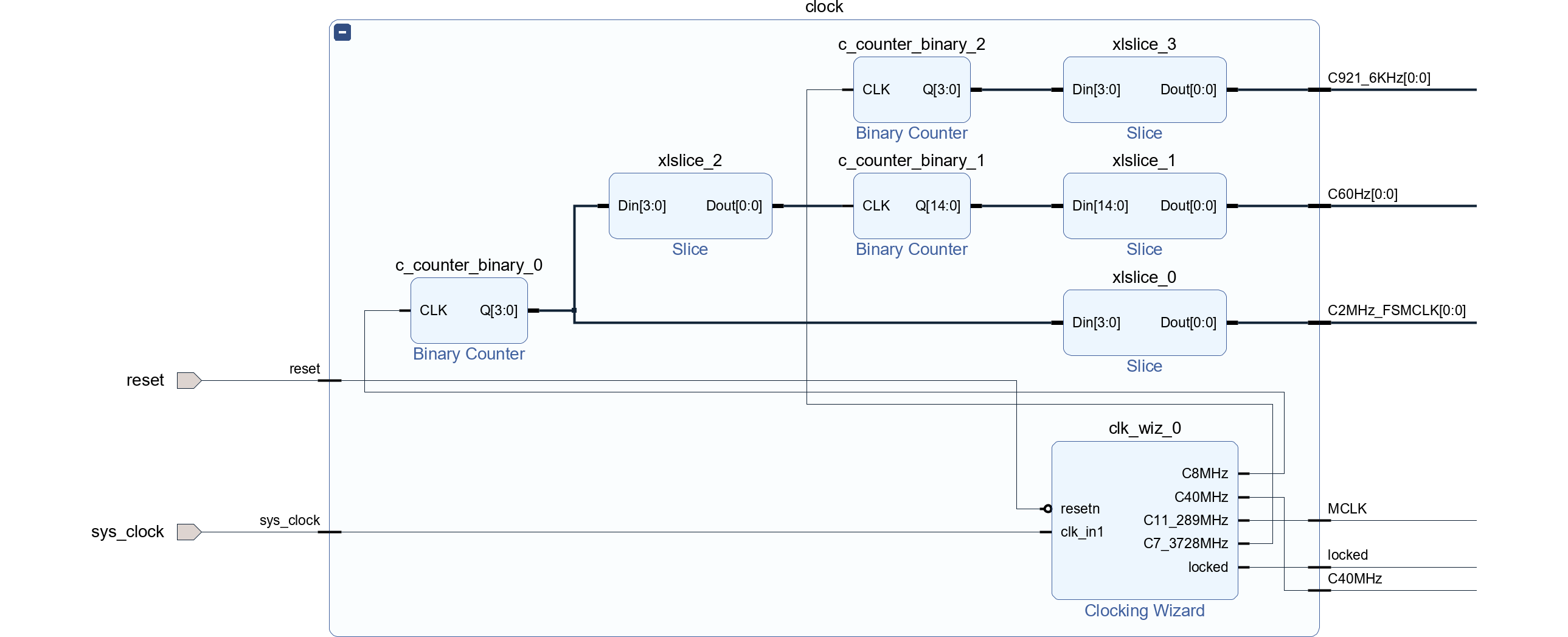

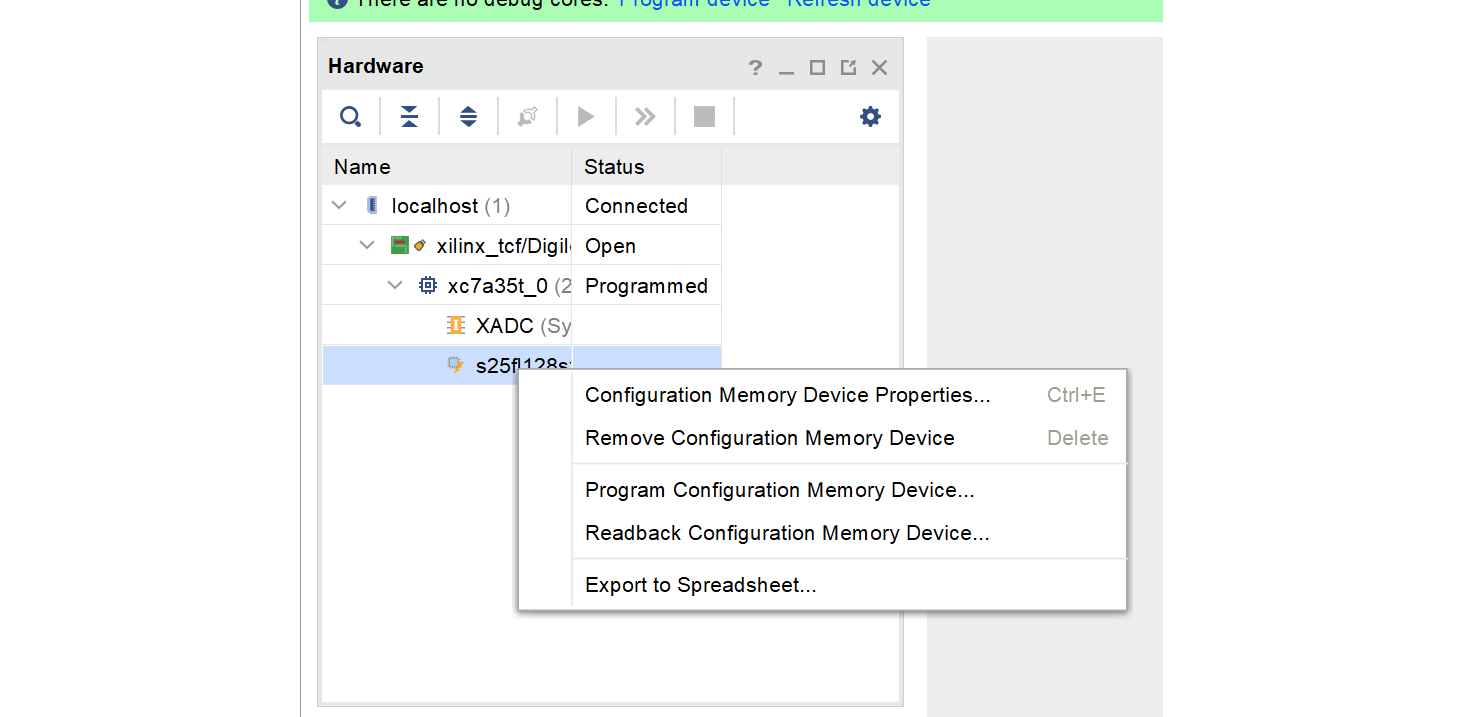

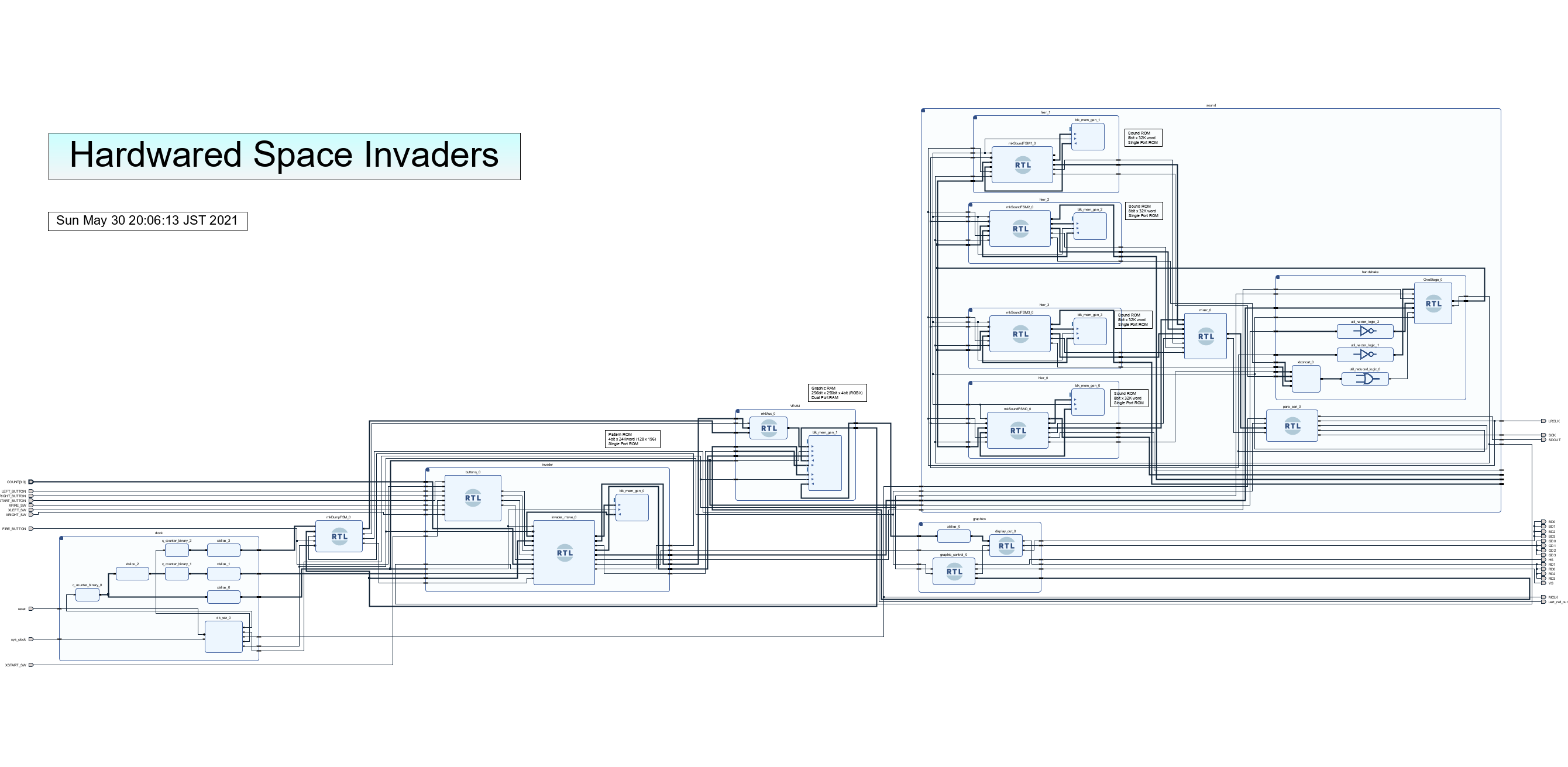

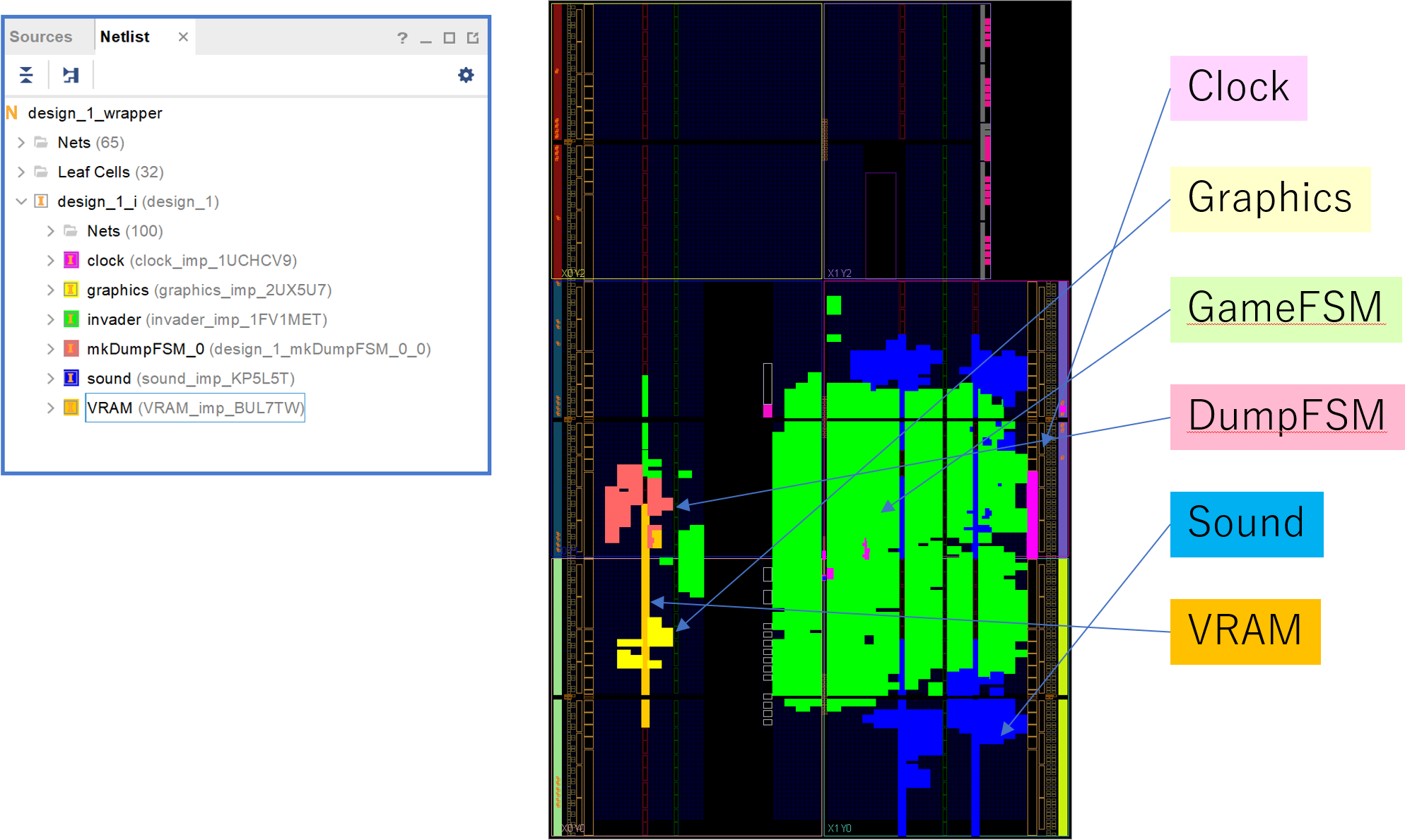

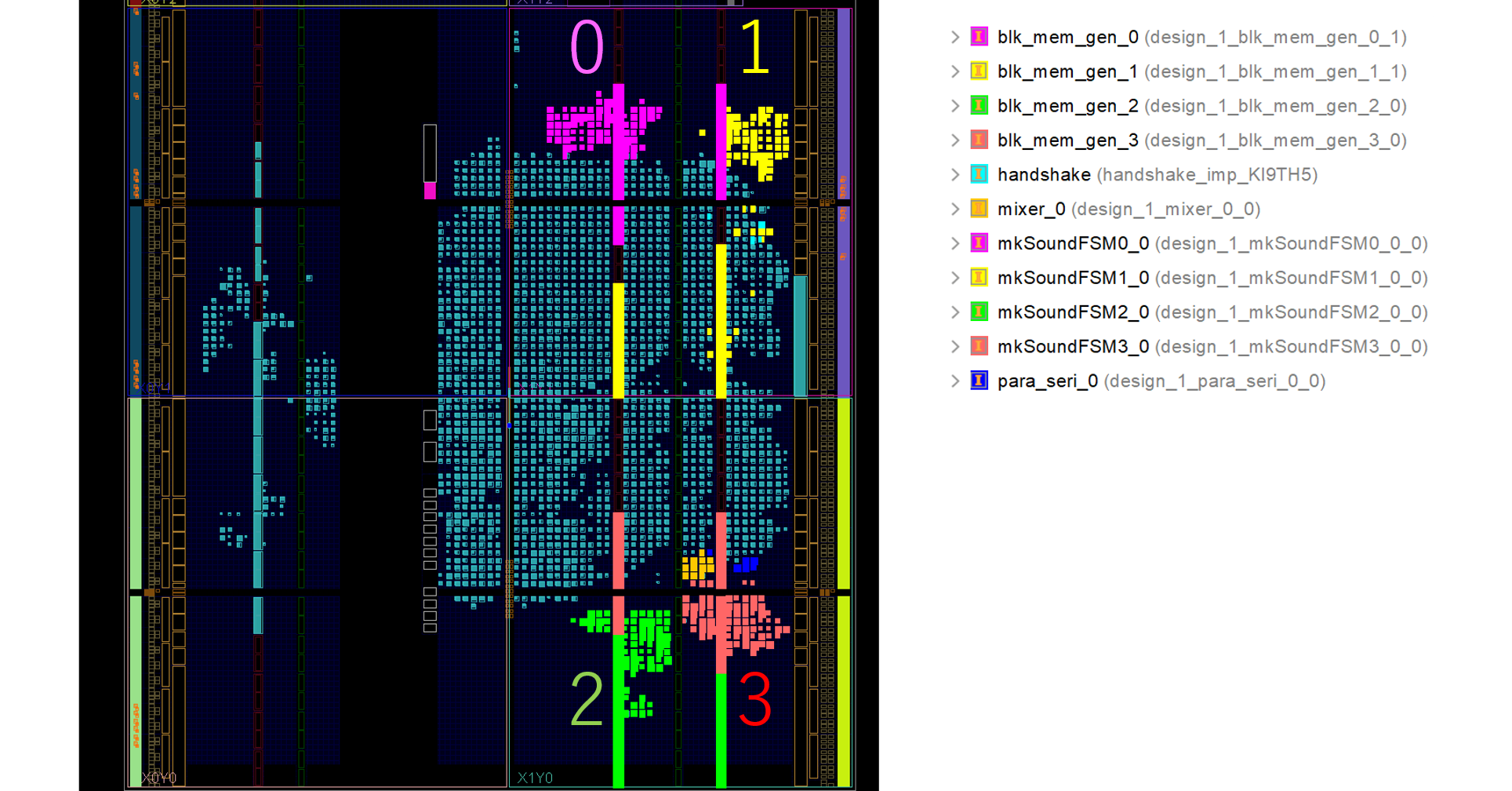

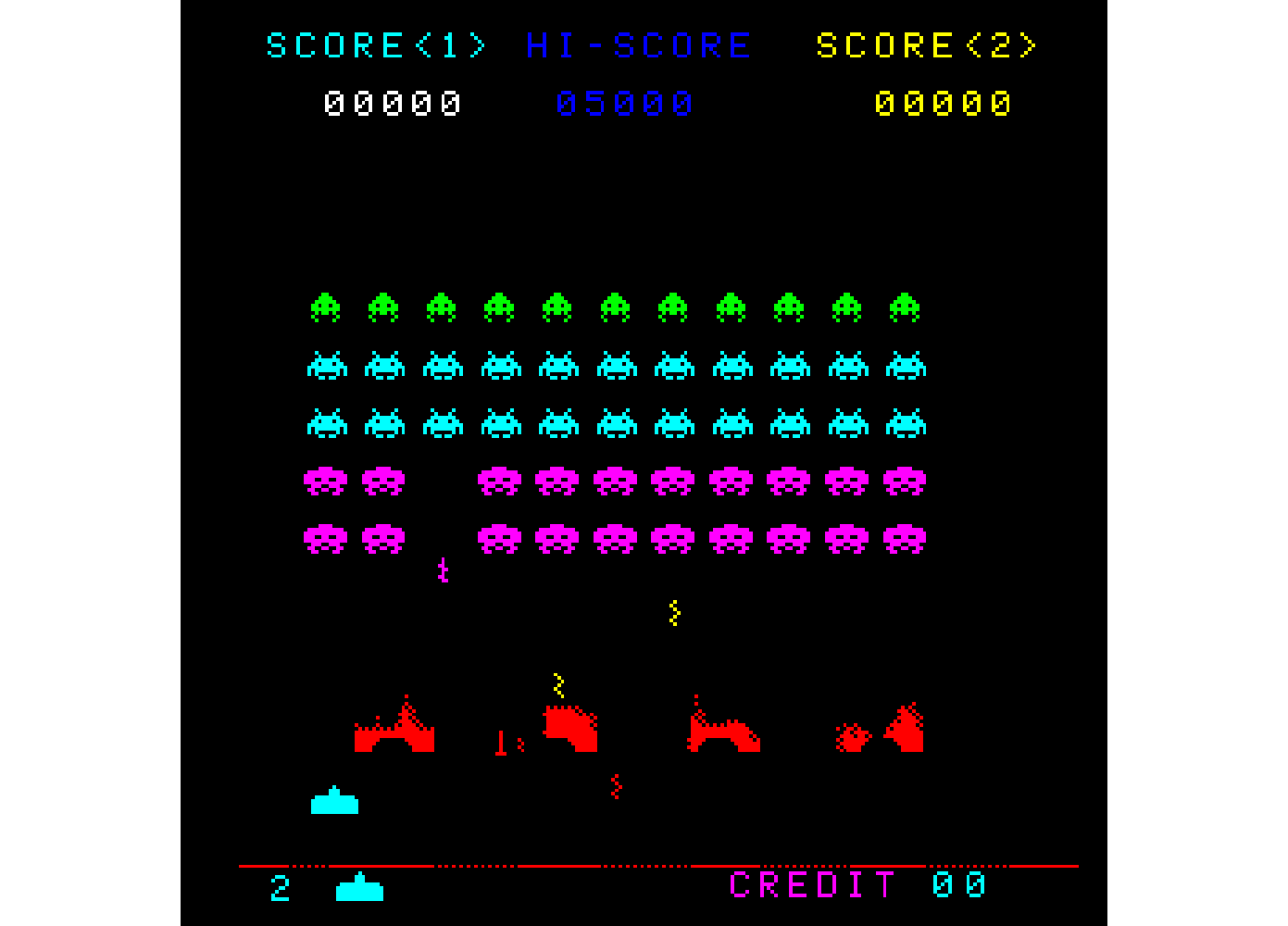

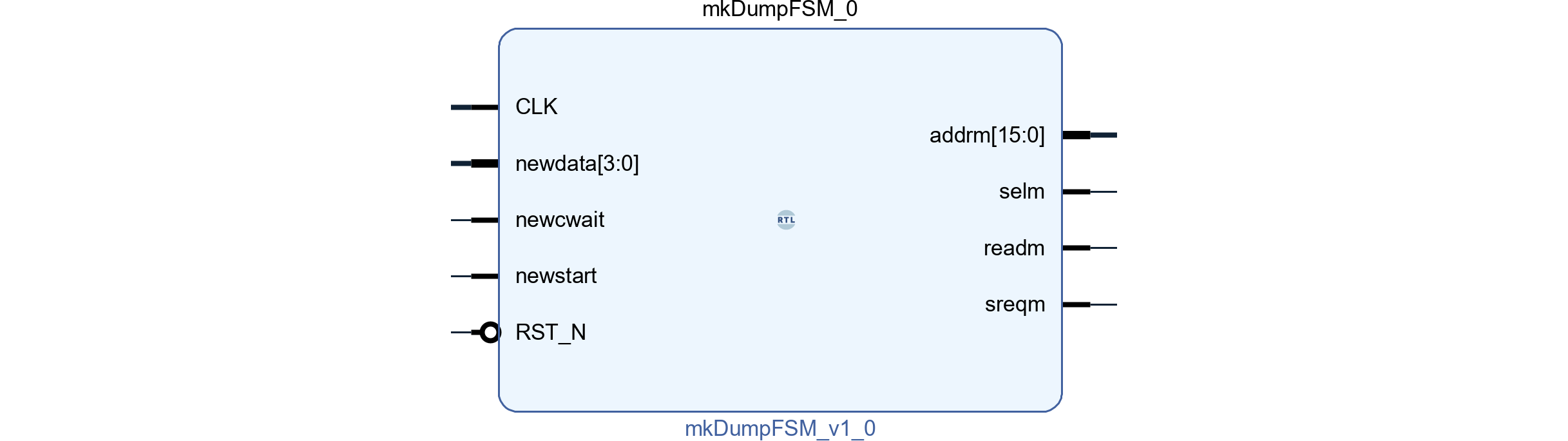

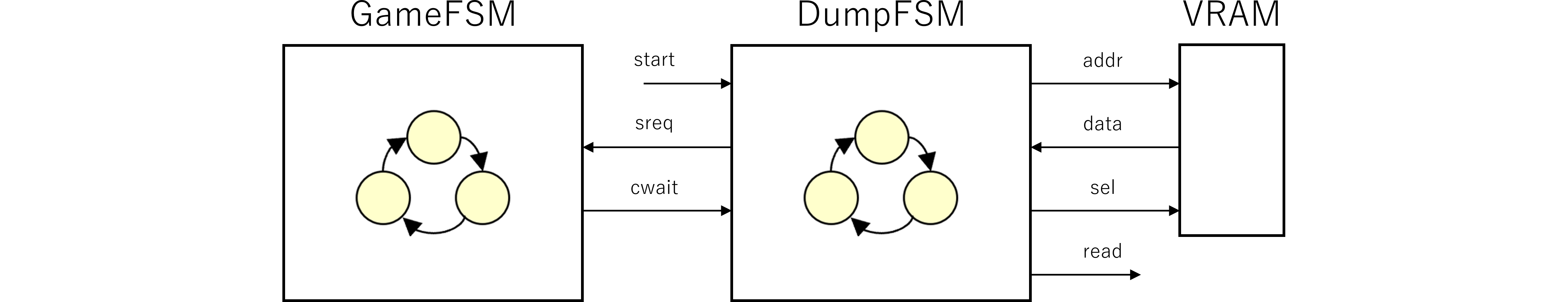

システム構成図

図405.1 システム構成図

図405.1 システム構成図

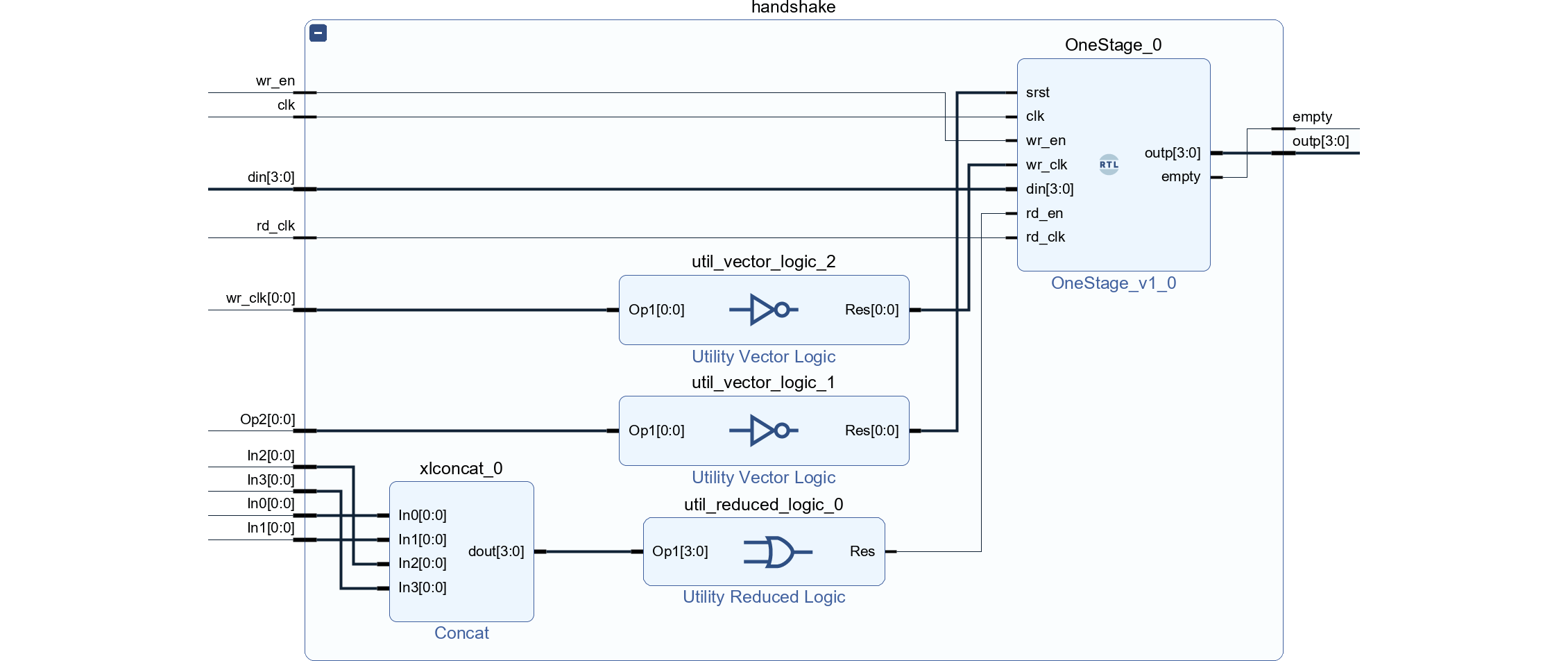

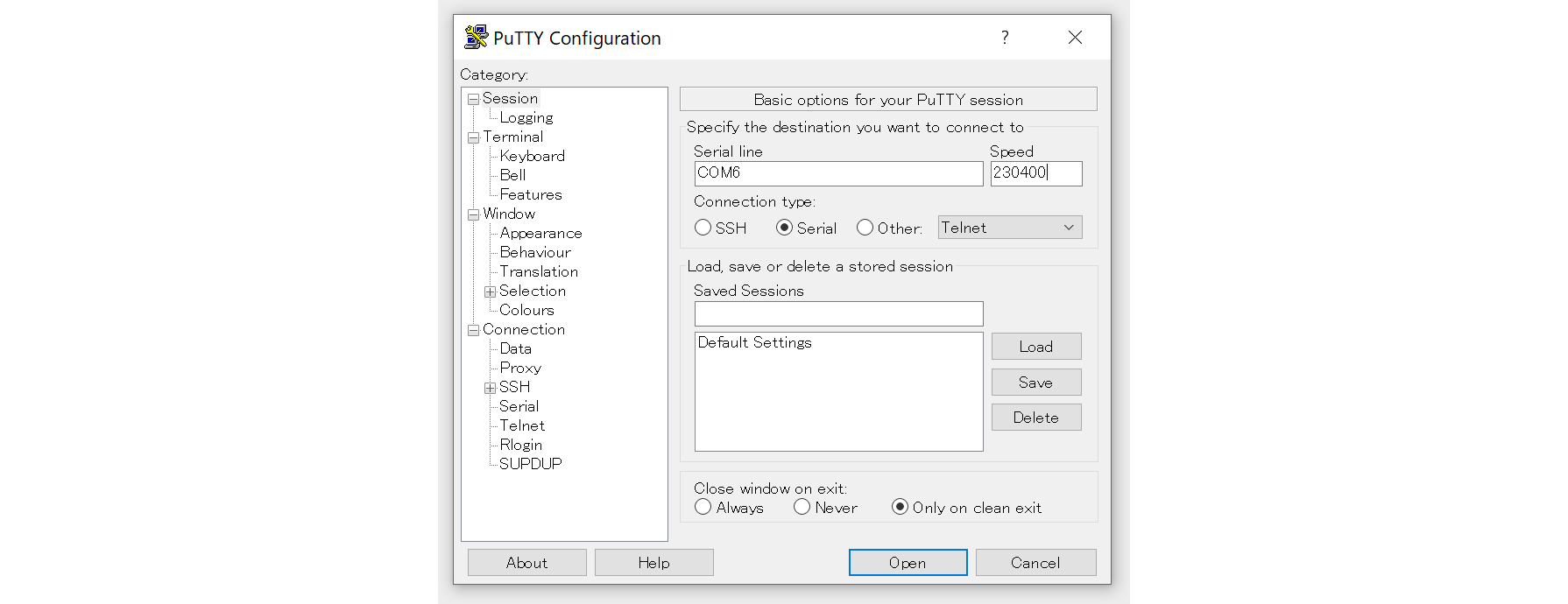

ハンドシェークアルゴリズム

以下に処理のハンドシェークを示します。

- ボード上のスイッチが押されstart信号が出力される。

- メモリダンパはstartに基づき、sreqを出力し、GameFSMに停止を要求。

- GameFSMは停止要求の有無に関わらず、フレームの最後で60Hzの立ち上がりを待つ。その際にcwaitを出力。

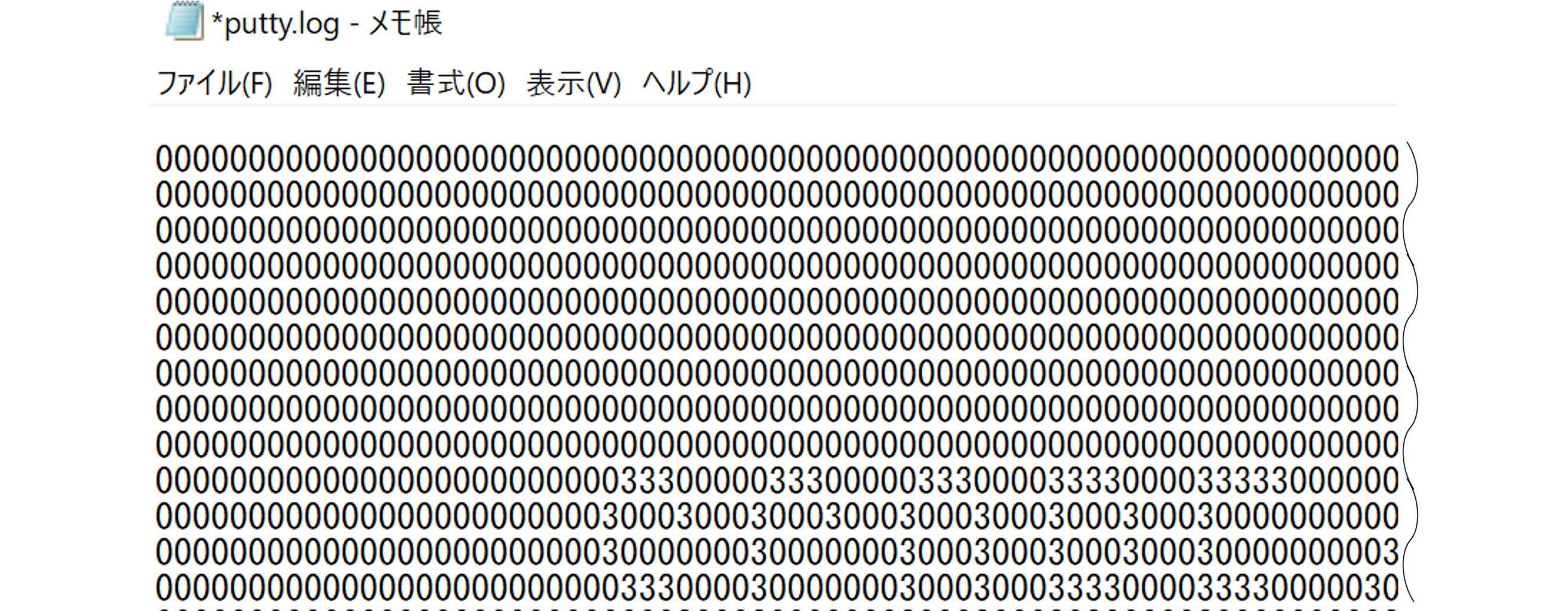

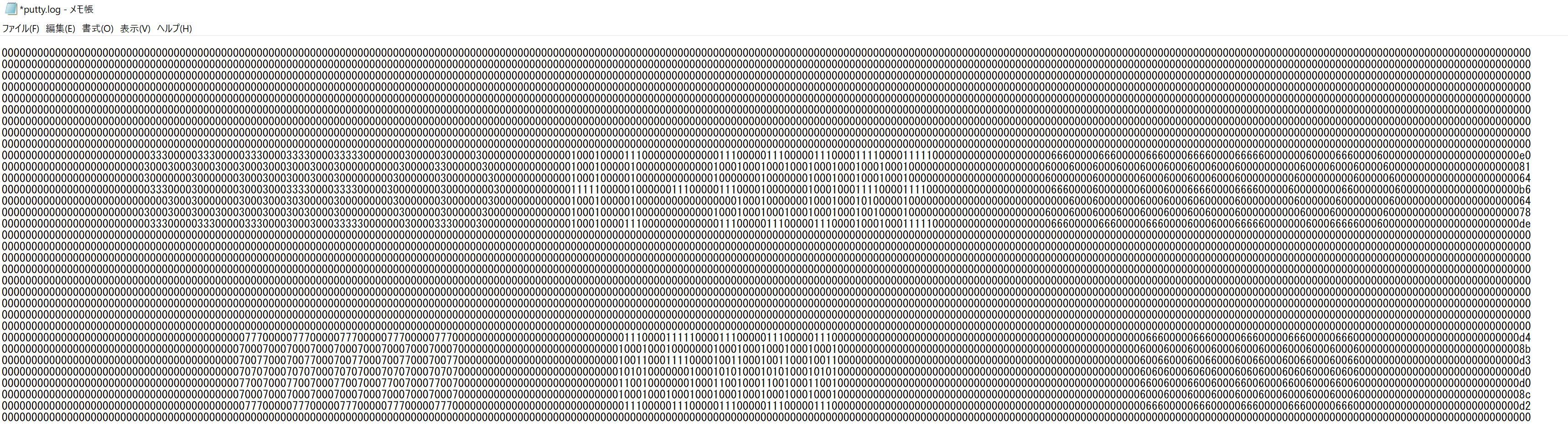

- メモリダンパはcwait(=GameFSMの停止)に基づき、以下のメモリダンプ動作をアドレス分だけ繰り返し。

- selをTrueにしてバス権(アドレス権)を取得

- アドレスを出力

- データを取得

- アスキー化してシリアルデータとして出力

- メモリダンパは終了時にsreqをネゲート。

- GameFSMはsreqがネゲートされるのを待ち、cwaitをネゲートしフレーム先頭から再開。

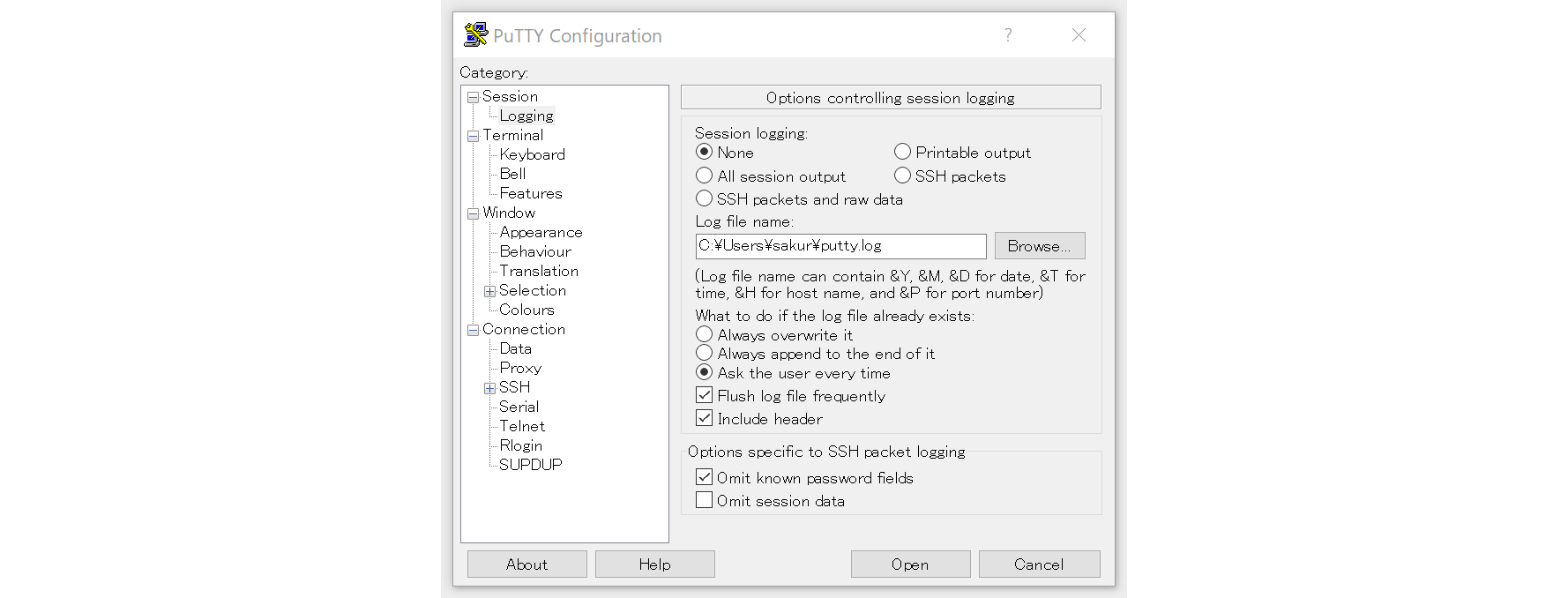

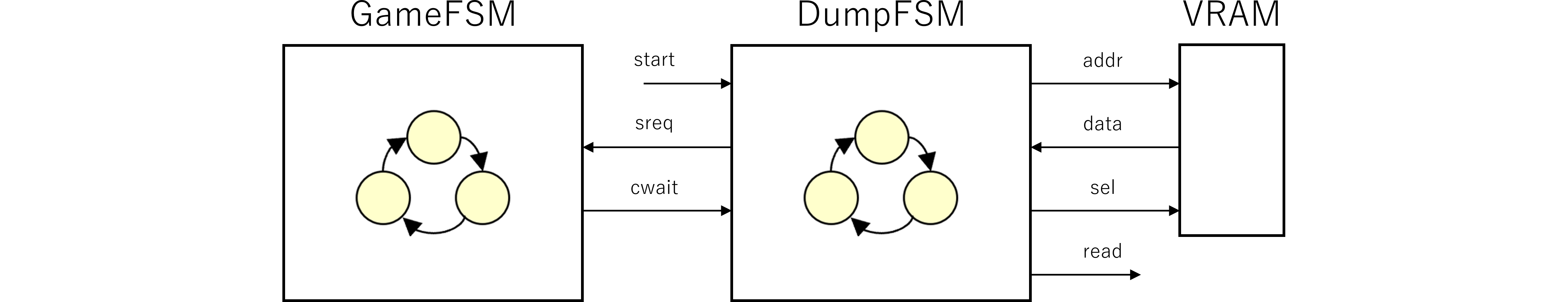

図405.2 タイミングチャート

図405.2 タイミングチャート

ゲームFSM側のBSVコードの修正

修正したGameFSM.bsvのウエイトルーチンを示します。

GameFSM.bsv

// 時間待ち

function Stmt wait_timer(

UInt#(12) count

);

return (seq

testOut <= True;

repeat(pack(extend(count))) seq

await(tic == 0);

await(tic == 1 && sreq == 0);

endseq

testOut <= False;

endseq);

endfunction

元々のtest出力信号(wait時を示す)testOut信号をそのままcwait(ゲームFSMのwaitを示す)として使用します。

元々は、60Hzの立下りを

await(tic == 0);

このように待った後、立ち上がりに同期して

await(tic == 1);

このように、ウエイトをリリースする(ウエイトルーチンから抜ける)仕様でした。今回それに加えて、メモリダンプからの停止要求がリリースされていることを

await(tic == 1 && sreq == 0);

このようにAND条件で加えました。これにより、ウエイトしている状態は元々testOut(=cwait)として出力されていたため、それを用いてメモリダンプの開始信号としています。

GameFSMのインタフェースにメモリダンパからの停止要求信号sreqを加えます。

GameFSM.bsv

(* prefix="" *)

method Action sreqm(Bit#(1) in_sreq);

次にワイヤ定義を記述します。

GameFSM.bsv

Wire#(Bit#(1)) sreq <- mkWire;

最後にメソッド定義を示します。

GameFSM.bsv

method Action sreqm(Bit#(1) in_sreq);

sreq <= in_sreq;

endmethod

前のブログ

次のブログ

前のブログ

次のブログ