|

20 |

FM-7 ROM吸出し器の改版 (6) |

|

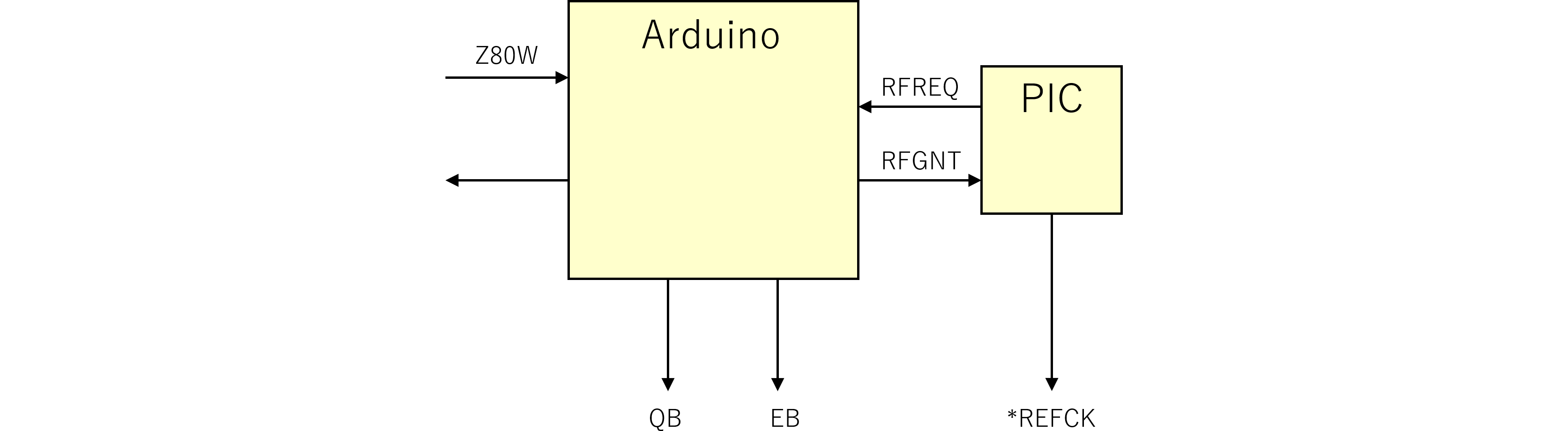

Arduino自身によるリフレッシュ

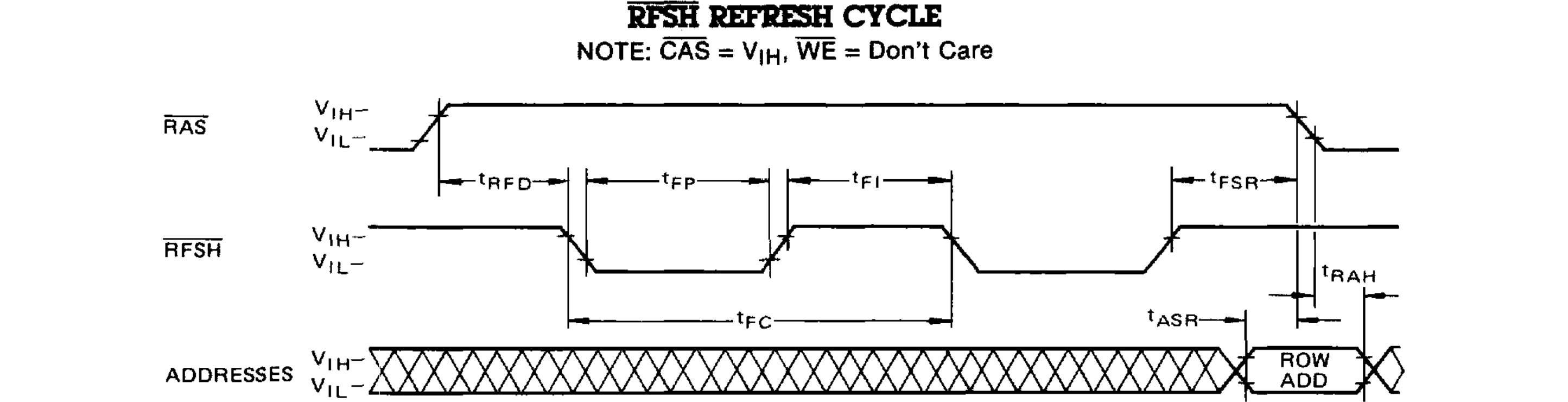

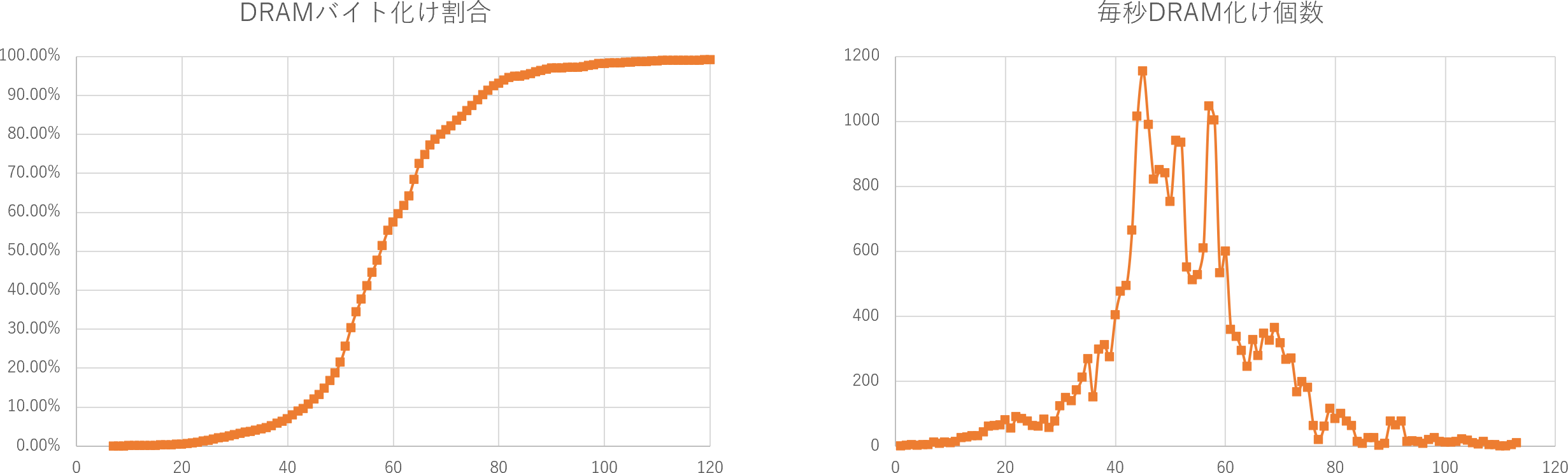

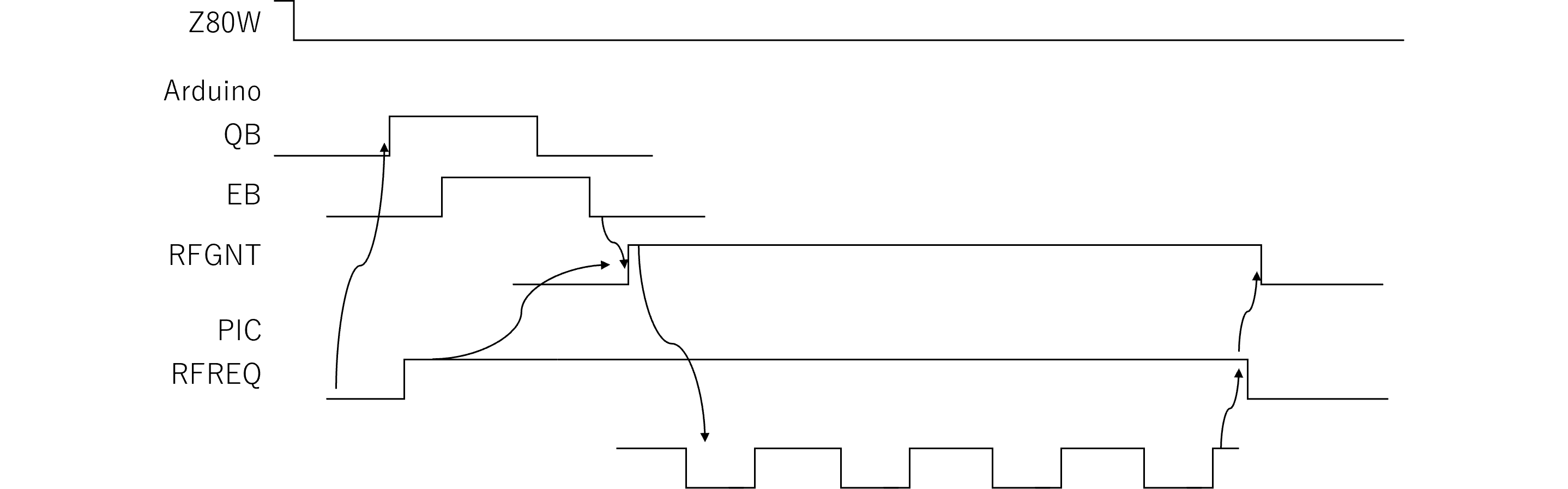

DRAMリフレッシュ手法を再考しました。PICでの割込みもArduinoでの割込みも、性能は別として論理的には同じように動作するはずです。そこで、PICで実装する前に、試行としてArduinoに割込みを入れてリフレッシュする方法を検討します。DRAMのリフレッシュタイミング制約によれば16.5 usecに1回リフレッシュパルスを入れる必要があります。Arduino 日本語リファレンスを探したのですが、マイクロ秒で割込みを入れられる関数は無いようでした。このMsTimer2だと、1 msecで割込みを入れて、その代わり、一回の割込みで64回のリフレッシュパルスを発行することになります。

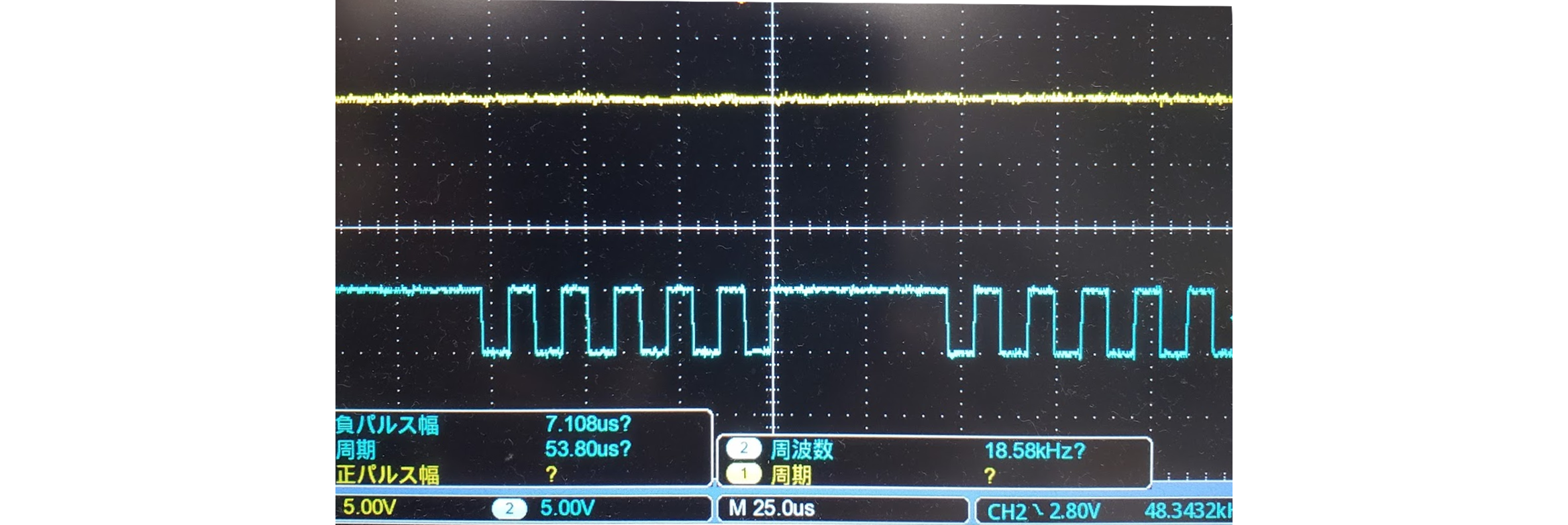

その後、FlexTimer2という、より自由度の高いタイマーが見つかったので、こちらを試します。DRAMのリフレッシュタイミング制約から以下の表261.1を作成しました。これに従い、実験によりタイマを決定します。

| 解像度 | 1割込みのリフレッシュ回数 | 周期 |

|---|---|---|

| 64,000 | 1 | 15.6 usec |

| 32,000 | 2 | 31.3 usec |

| 16,000 | 4 | 62.5 usec |

| 8,000 | 8 | 125 usec |

| 4,000 | 16 | 250 usec |

| 2,000 | 32 | 500 usec |

| 1,000 | 64 | 1 msec |

| 500 | 128 | 2 msec |

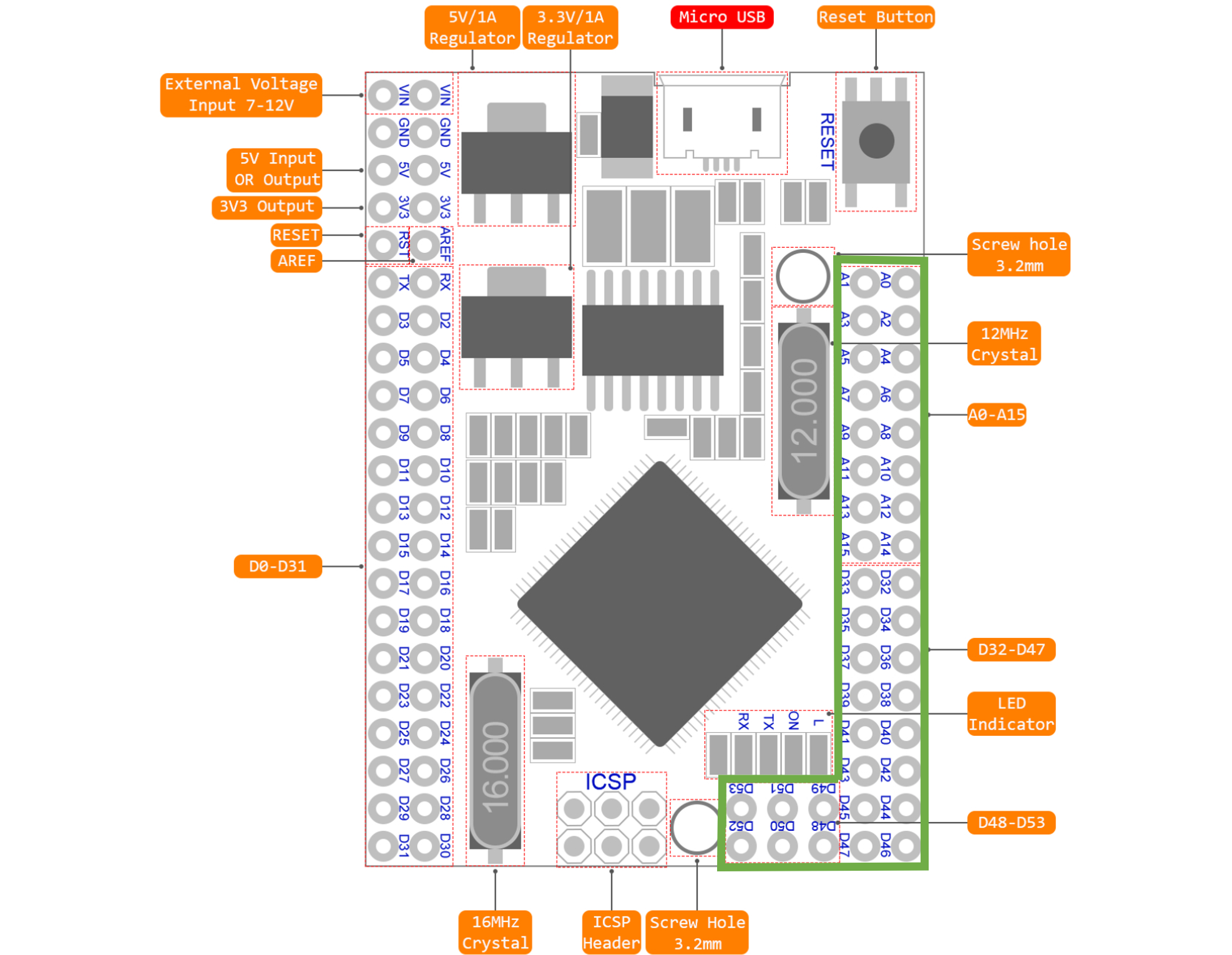

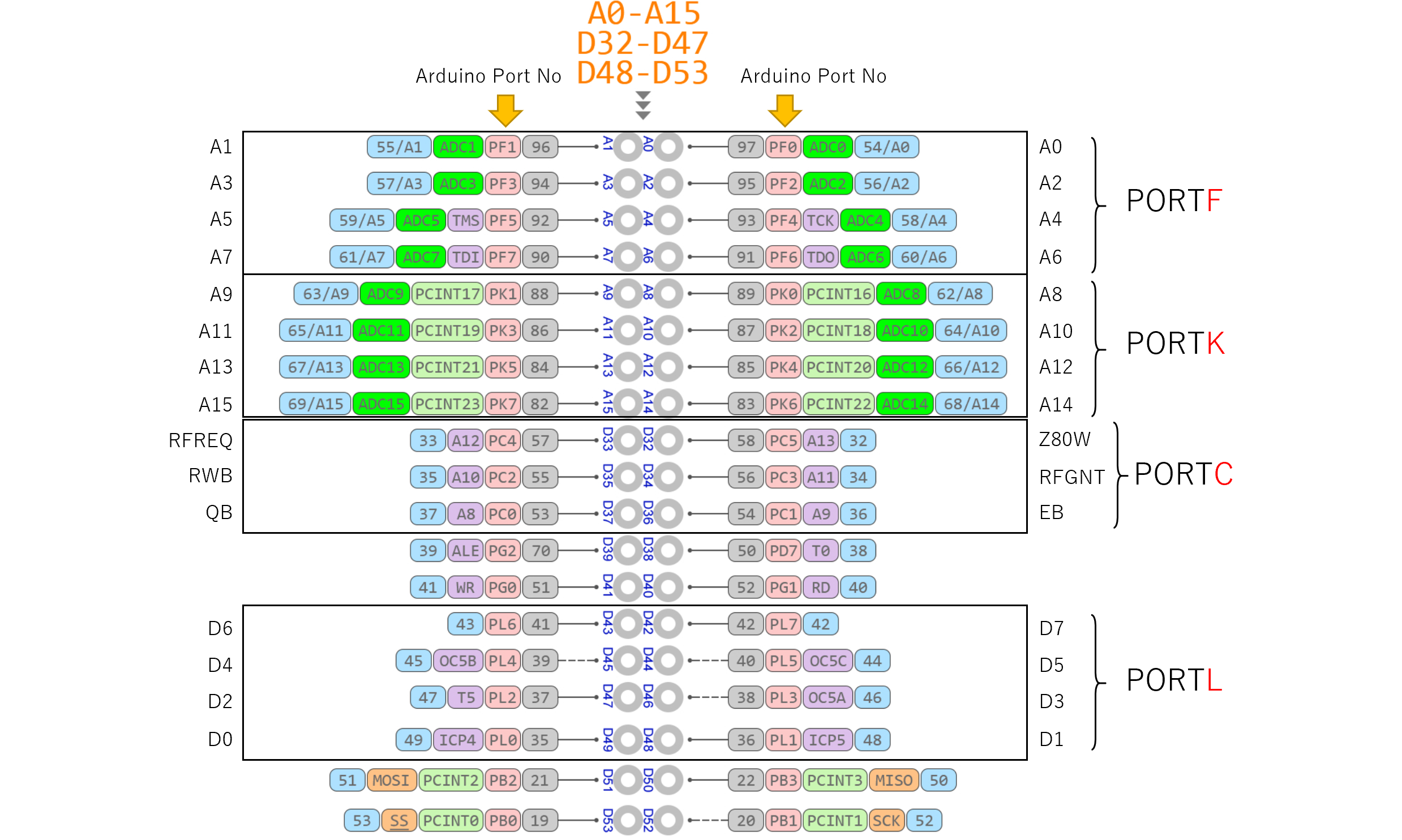

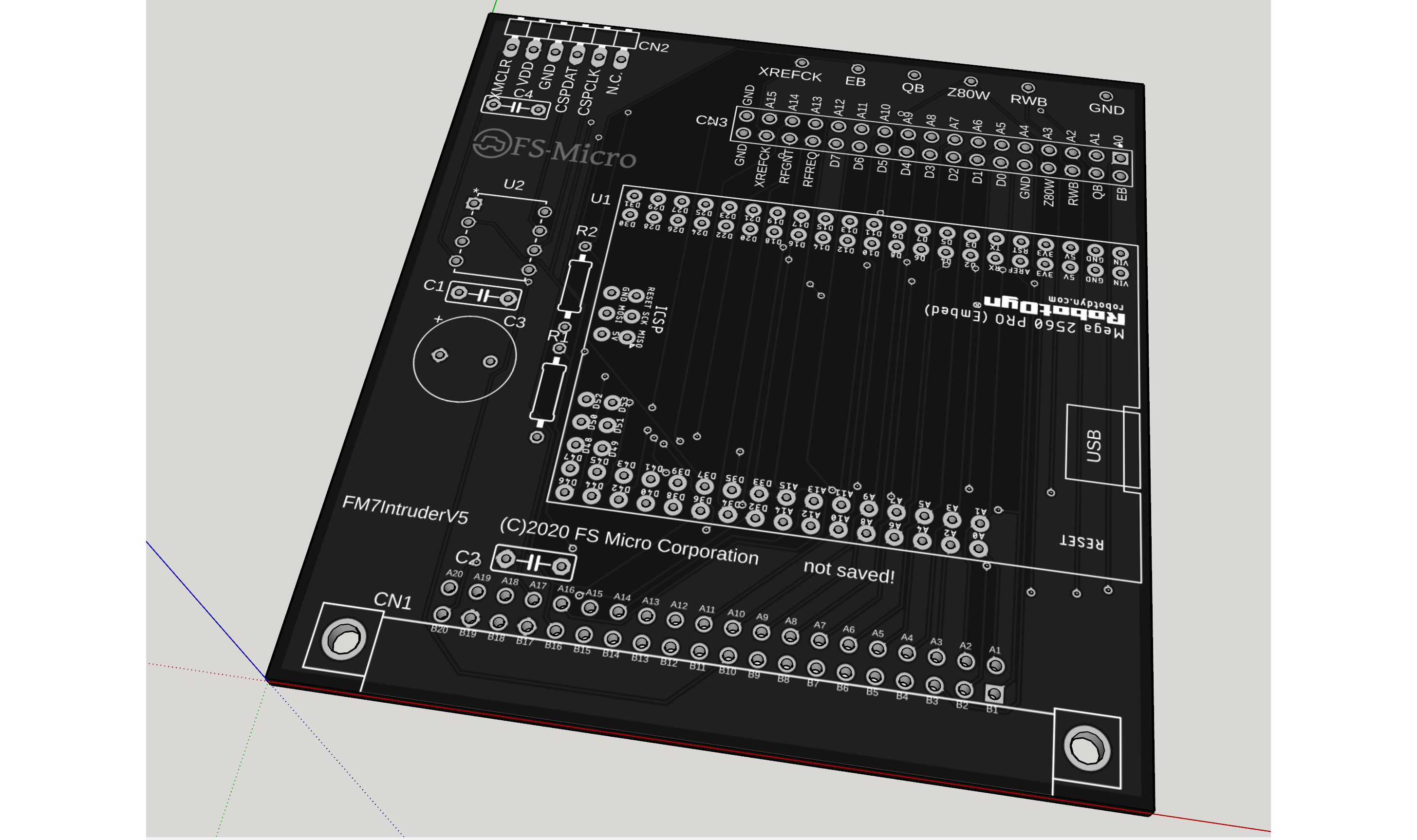

既存の基板のポートに対して、D44からZ80コネクタB18(*REFCK)に1本ジャンパー線を配線します。

#define XREFCK 44

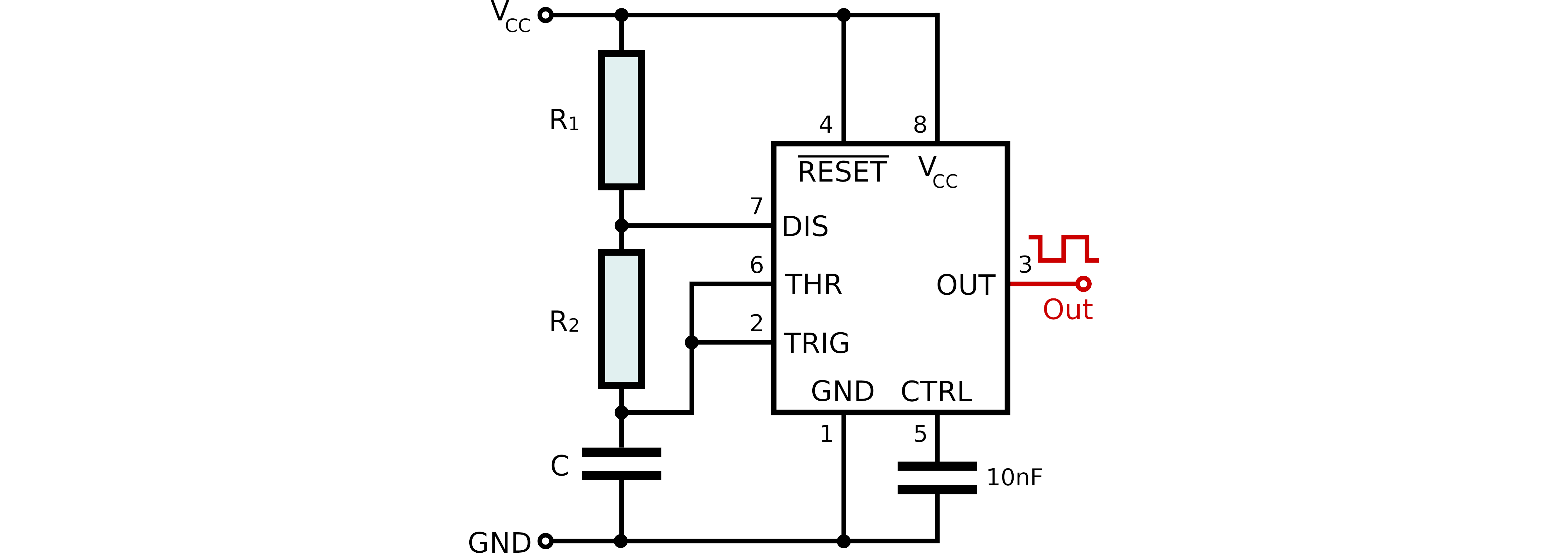

割込みをイニシャライズルーチンsetup()で設定します。ここでは解像度を8,000として、割込みを1/8,000 sec=125 usec毎にかけ、refresh関数を呼び出します。

FlexiTimer2::set(1, 1.0/8000, refresh); // call every 125usec "ticks"

また、リフレッシュルーチンは以下のとおりです。

void refresh() {

digitalWrite(XREFCK, LOW);

digitalWrite(XREFCK, HIGH);

digitalWrite(XREFCK, LOW);

digitalWrite(XREFCK, HIGH);

digitalWrite(XREFCK, LOW);

digitalWrite(XREFCK, HIGH);

digitalWrite(XREFCK, LOW);

digitalWrite(XREFCK, HIGH);

digitalWrite(XREFCK, LOW);

digitalWrite(XREFCK, HIGH);

digitalWrite(XREFCK, LOW);

digitalWrite(XREFCK, HIGH);

}

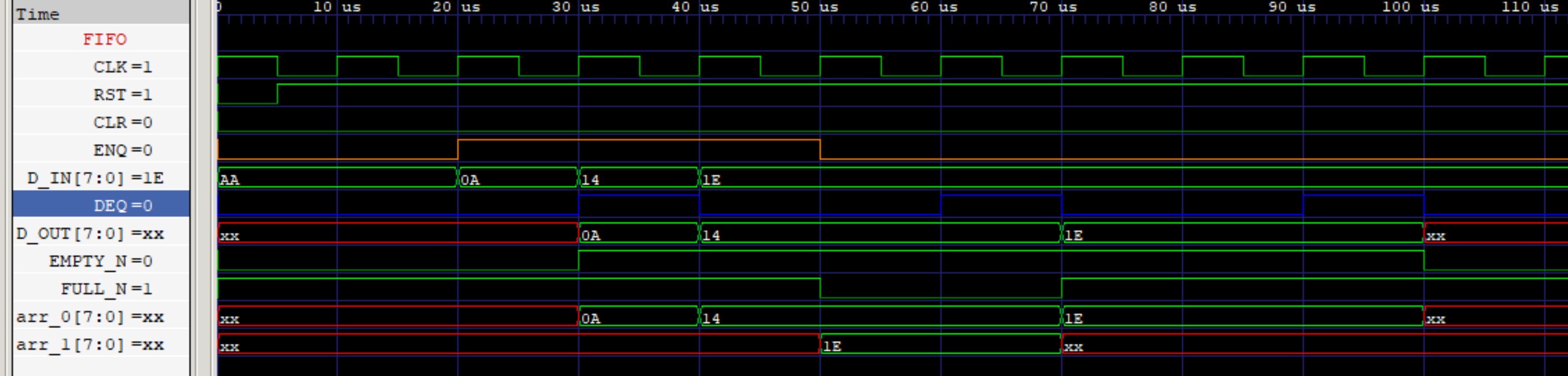

このスケッチを実行した波形を図261.1に示します。

評価プログラムを用いた実験結果は、熱はかけていないものの288秒で打ち切るまでノーエラーだったので、リフレッシュ回路は一応OKと判断します。ただし、DRAMリフレッシュのマージンに頼った実力OKの方式です。能力の大方がリフレッシュという効率も悪い方式なので、PICで改善することを期待します。