|

1 |

グラフィックディスプレイコントローラの設計 |

|

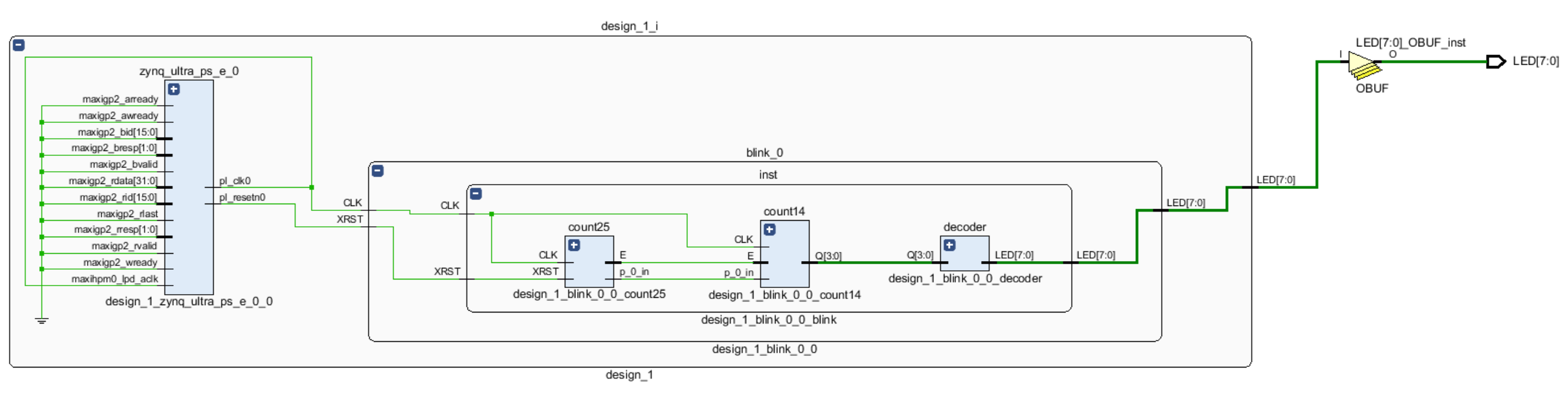

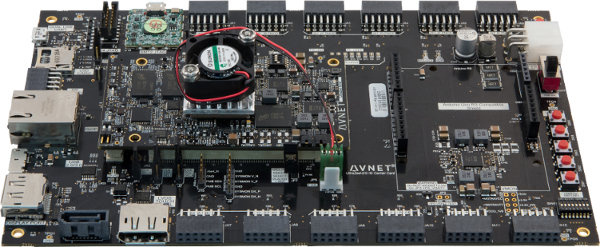

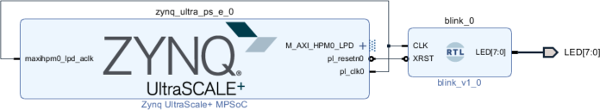

高機能なFPGAボードを使って、Lチカではあまりにつまらないため、次にグラフィックディスプレイコントローラの設計を行います。

グラフィックディスプレイの解像度は様々なものがあり、タイミング設計の際に参考になるサイトをご紹介します。

http://tinyvga.com/vga-timing

今回はSVGAのグラフィックディスプレイの設計を行います。

http://tinyvga.com/vga-timing/800x600@60Hz

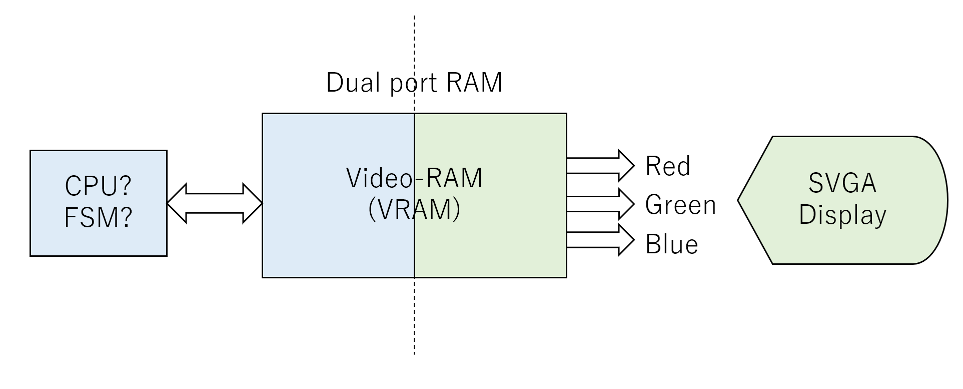

基本的には、横800dotかける縦600dotかける色深度、例えば8色であれば3bitの情報を記憶するメモリが中心となります。これを通常VRAM (Video RAM)と呼びます。

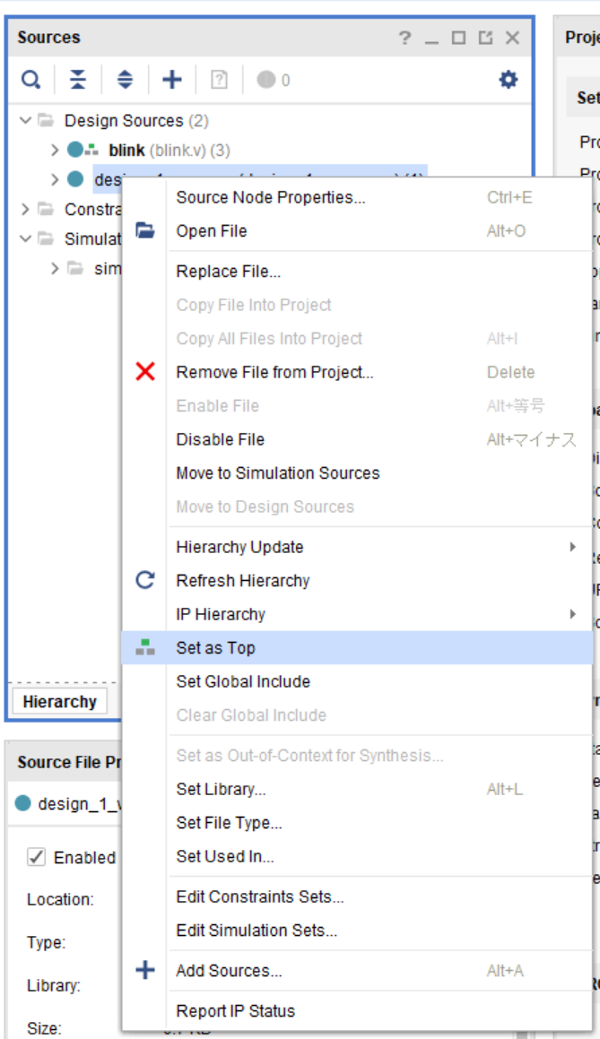

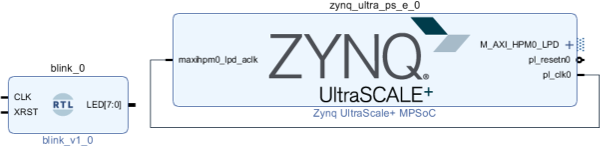

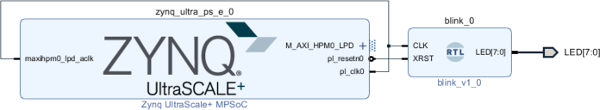

少々問題になるのは、VRAMは2つのバスマスタによりアクセスされることです。第1にグラフィックディスプレイコントローラ(GDC)、第2に描画マスタであるCPU。ただし、描画マスタはCPUとは限らず、ハードウェアでも構いません。問題は、両者が同時に同じポートにアクセスすると、VRAMのポートがひとつしかない場合には待たされることになります。GDCはディスプレイのタイミングに合わせて画像を読み出す必要があるため、待たすことができません。従ってCPUを待たすことになります。

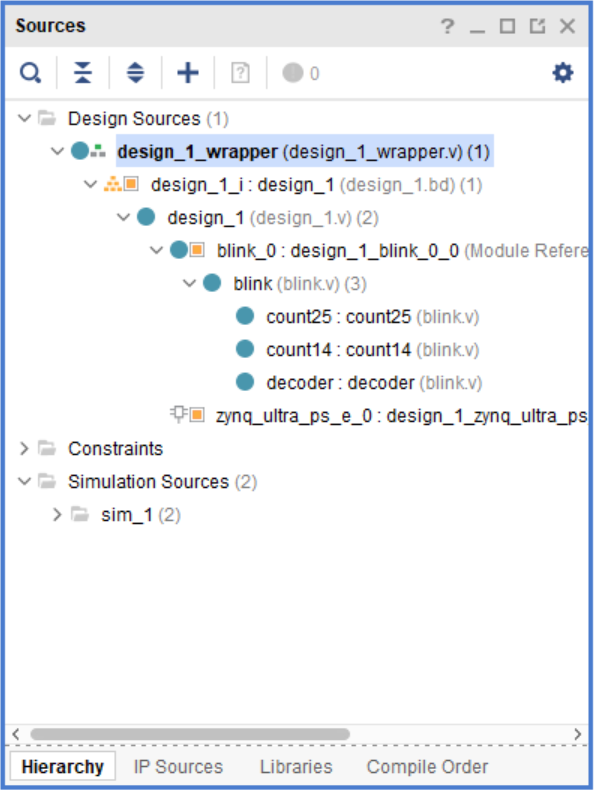

一方、VRAMのポートを増やして2つにすれば、この問題は解決することができます。これをデュアルポートメモリと呼びます。以下の図は非同期のデュアルポートメモリを用いたディスプレイ表示装置の例で、ブルーのクロックドメインとグリーンのクロックドメインの周波数は特に関係がありません。グリーンは前記のようにSVGAのタイミングで動作します。

シングルポートメモリを2つ並列に実装し、書き込みは同じデータを両方のメモリに書くことでデュアルポートメモリと見せることができます。これは2つのマスタのうち、GDCは読み出しのみを行い、書き込みを行わないことから可能です。

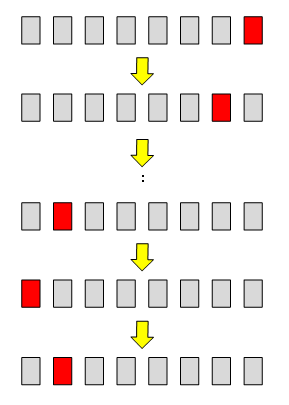

デュアルポートメモリからの読み出しが安定して継続できるようにラインバッファを持つことを考えます。 これはFIFOにより実装します。具体的には2ラインのラインバッファを持ち、1ライン詰めたところで、書き込みと読み出しの平均スループットが同じになるように釣り合わせれば、FIFOオーバランもアンダーランも起きないと考えられます。