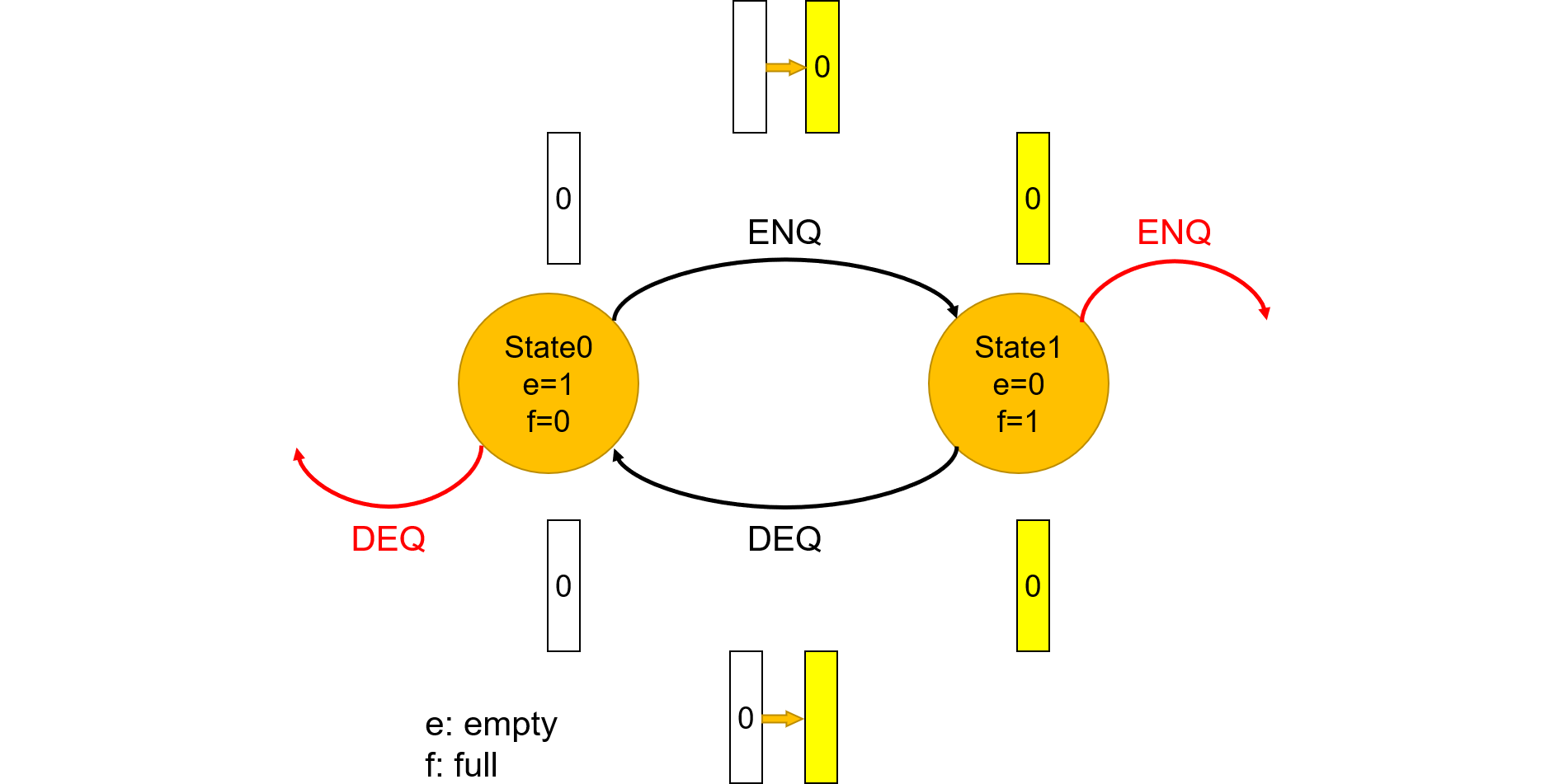

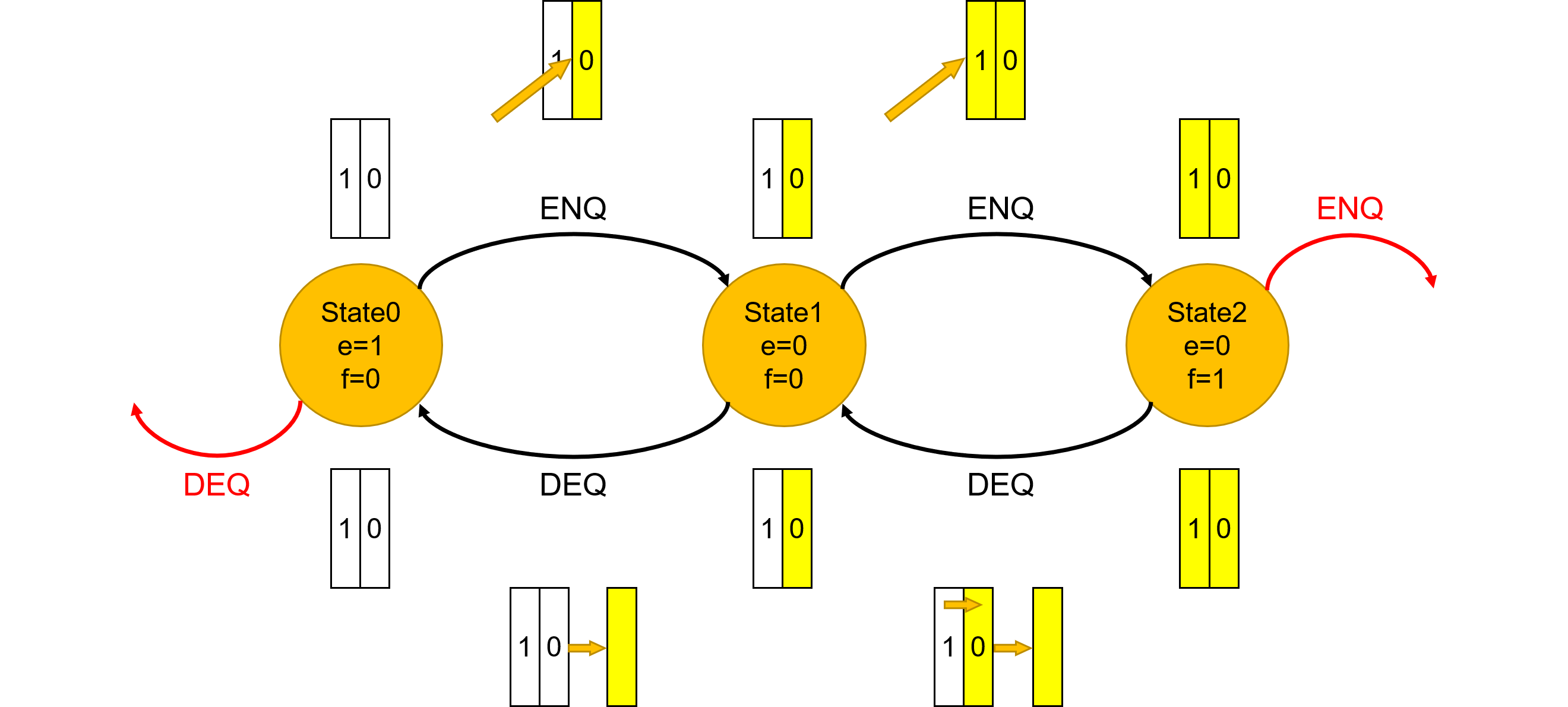

2段FIFOの検討(4)

過去記事で紹介したPLDツールのcuplを用いてespressoによる論理圧縮を行い、手で実施した論理圧縮が合っているかを確認します。

d0diの入力ファイルです。d0diはNo.2とNo.8の時にアサートなので、

d0di = (!deq & enq & empty & !full) /* 2 */

# (deq & enq & !empty & !full); /* 8 */

とします。ただしそれ以外にもD.C.となる場合は多く、No.2に対してはNo.4, 14, 16、No.8に対してはNo. 4, 7, 3を加えて論理圧縮をかけます。ただし、論理圧縮は機械でできるものの、有効なD.C.ケースを加える部分は手で行う必要があります。

d0didc = (!deq & enq & empty & !full) /* 2 */

# (deq & enq & empty & !full) /* 4 */

# (!deq & enq & empty & full) /* 14 */

# (deq & enq & empty & full) /* 16 */

# (deq & enq & !empty & !full) /* 8 */

# (deq & enq & empty & !full) /* 4 */

# (deq & !enq & !empty & !full) /* 7 */

# (deq & !enq & empty & !full); /* 3 */

cuplの圧縮結果を示します。

d0di =>

deq & !empty & enq & !full

# !deq & empty & enq & !full

d0didc =>

deq & !full

# empty & enq

これは手圧縮の前ページの結果d0di = (ENQ && empty == 1) || (DEQ && full == 0)と一致しています。しかしながら、両方共D.C.ケースを手で加える部分は共通なのでその妥当性は証明されず、論理圧縮のみを検証したことになります。

以下同様に、d0d1の入力は11ですが、これにD.C.ケースである12, 15, 16を加え論理を簡単化します。

d0d1 = (deq & !enq & !empty & full); /* 11 */

d0d1dc = (deq & !enq & !empty & full) /* 11 */

# (deq & enq & !empty & full) /* 12 */

# (deq & !enq & empty & full) /* 15 */

# (deq & enq & empty & full); /* 16 */

cuplの圧縮結果を示します。

d0d1 =>

deq & !empty & !enq & full

d0d1dc =>

deq & full

これは、手圧縮の結果d0d1 = DEQ && full == 1と一致しています。

次にd0hの論理は5, 6, 9ですが、これにD.C.ケースである10を加え論理を簡単化します。

d0h = (!deq & !enq & !empty & !full) /* 5 */

# (!deq & enq & !empty & !full) /* 6 */

# (!deq & !enq & !empty & full); /* 9 */

d0hdc = (!deq & !enq & !empty & !full) /* 5 */

# (!deq & enq & !empty & !full) /* 6 */

# (!deq & !enq & !empty & full) /* 9 */

# (!deq & enq & !empty & full); /* 10 */

cuplの圧縮結果を示します。

d0h =>

!deq & !empty & !full

# !deq & !empty & !enq & full

d0hdc =>

!deq & !empty

これは手圧縮の結果d0h = !DEQ && empty == 0と一致しています。

最後にd1diの論理は6, 12ですが、これにD.C.ケースである8, 10を加え論理を簡単化します。

d1di = (!deq & enq & !empty & !full) /* 6 */

# (deq & enq & !empty & full); /* 12 */

d1didc = (!deq & enq & !empty & !full) /* 6 */

# (deq & enq & !empty & full) /* 12 */

# (deq & enq & !empty & !full) /* 8 */

# (!deq & enq & !empty & full); /* 10 */

cuplの圧縮結果を示します。

d1di =>

!deq & !empty & enq & !full

# deq & !empty & enq & full

d1didc =>

!empty & enq

これは手圧縮の結果d1di = ENQ && empty == 0と一致しています。

前のブログ

次のブログ

前のブログ

次のブログ