|

7 |

BSVの設計トライアル |

|

スペースインベーダーのモジュールの入れ替え

過去にスペースインベーダーをRTLで開発しました。今回はBSVのトライアルとして既存のverilogモジュールの入れ替えを実施します。小さめのFSMであるサウンドFSMを入れ替えますが、合わせて仕様も高級なものにしようと思います。RTLで記述したときは、サウンドチャネルは1個で、優先度判定を行いサウンド割込みを行いました。今回は、サウンドチャネルを複数持って、サウンド重畳を行うことを考えます。そのため、複数の音を出し音量を平均化するような、サウンドミックス回路を新設します。

サウンドチャネルの決定

さて、音は以下の10種類ですが、同時発生を考えて、自機音、インベーダ音1, 2、UFO音の4チャネルとします。また、サウンド演奏中に割込みが入るため、プリエンプティブに設計する必要があります。

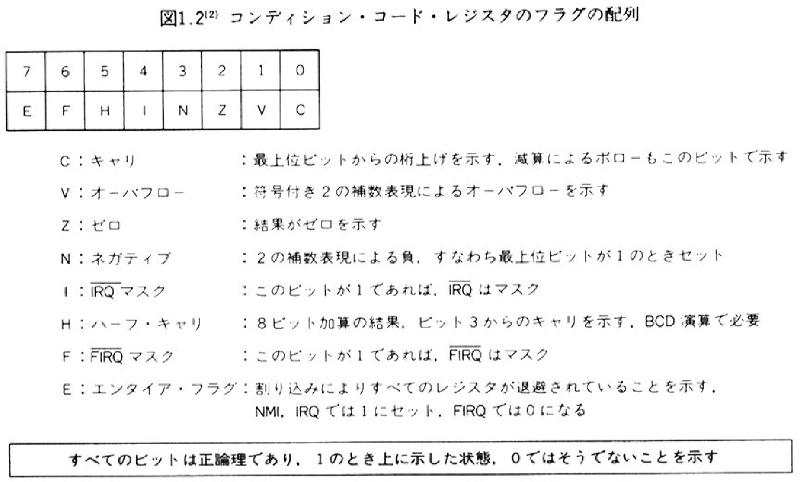

| サウンドの説明 | CODE番号 | サウンドチャネル | バイト数 | 先頭オフセット+16 | |

|---|---|---|---|---|---|

| ON | OFF | ||||

| 自機弾発射音 | 1 | ー | 自機音チャネル(#0) | 4,318 | 0 + 16 |

| 自機爆発音 | 2 | ー | 8,776 | 4,318 + 16 | |

| 自機増加音 | 9 | ー | 5,500 | 13,094 + 16 | |

| インベーダ爆発音 | 3 | ー | インベーダ音チャネル(#1) | 4,622 | 0 + 16 |

| インベーダ歩行音1 | 4 | ー | インベーダ音チャネル(#2) | 1,266 | 0 + 16 |

| インベーダ歩行音2 | 5 | ー | 1,570 | 1,266 + 16 | |

| インベーダ歩行音3 | 6 | ー | 1,570 | 2,836 + 16 | |

| インベーダ歩行音4 | 7 | ー | 2,180 | 4,406 + 16 | |

| UFO爆発音 | 8 | ー | UFO音チャネル(#3) | 25,968 | 0 + 16 |

| UFO飛行音 | 10 | 16 + 10 | 1,846 | 25,968 + 16 | |

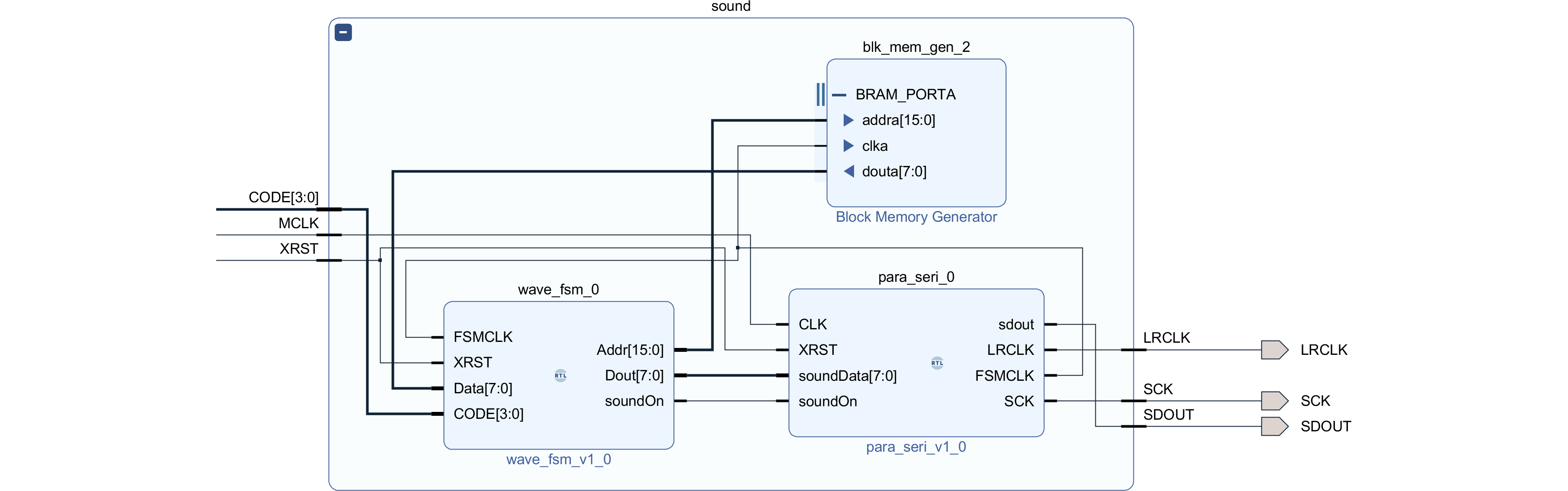

変更前後のブロック図

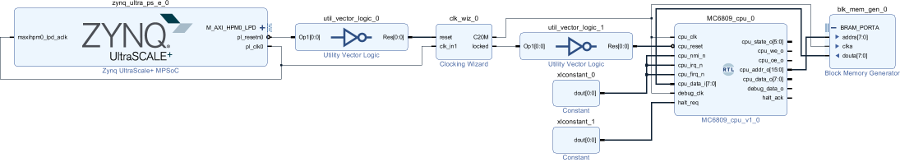

現状のRTL設計でのブロック図をVivadoで表示したものを図234.1に示します。

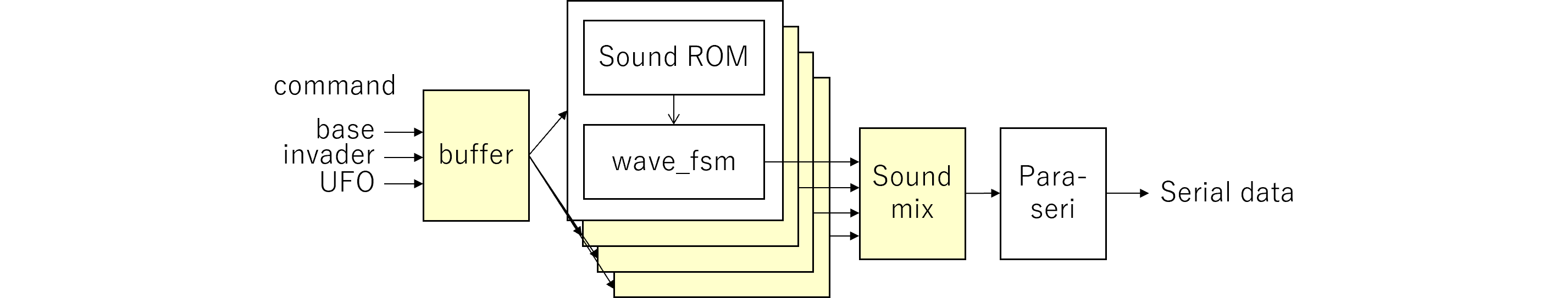

新仕様のブロック図は図234.2のようになります。色付けの部分が新規設計モジュールです。