|

7 |

BSVによるメモリダンプモジュールの設計 |

|

上位モジュールの設計

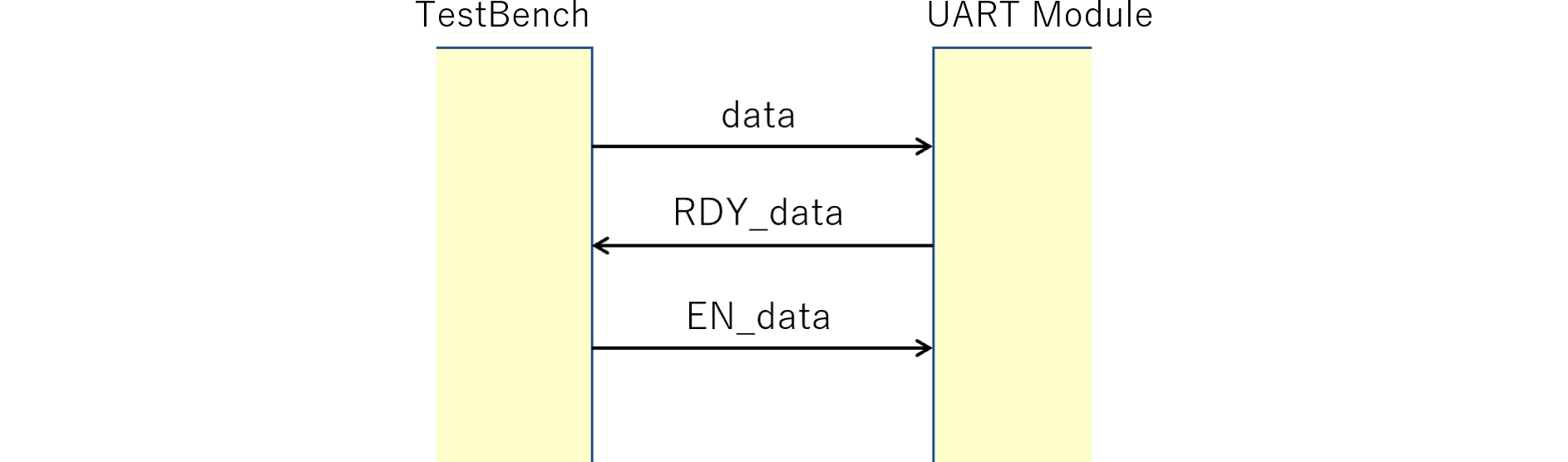

1バイトの送信はうまく行ったようなので、上位モジュールMemoryDumpを設計します。概略仕様を以下に示します。

- 1ワードが4bitで構成されるメモリをダンプします。

- メモリのアドレス0からの内容を65536ワード送信します。

- 256行×256列で送信し、1行毎にチェックサムを送信します。

- 1バイトのバイナリは表示可能な2バイトのアスキーコードに変換します。

- 行末は改行します。

メモリ空間は64Kバイトあります。以下にアルゴリズムをC likeの疑似コードにより示します。

疑似コード

int x, y, address;

byte data, checksum, upper, lower;

address = 0;

for (y=0 to 255) {

checksum = 0;

for (x = 0 to 255) {

data = memory[address++];

checksum += data;

data += (data >= 10) ? (-10 + "a") : "0";

uart.load(data);

}

upper = (checksum >> 4) & 8'h0f;

upper += (upper >= 10) ? (-10 + "a") : "0";

uart.load(upper);

lower = checksum & 8'h0f;

lower += (lower >= 10) ? (-10 + "a") : "0";

uart.load(lower);

uart.load(LF);

}