|

25 |

Pipeline processorの設計 (17) |

既存RISC-Vの研究

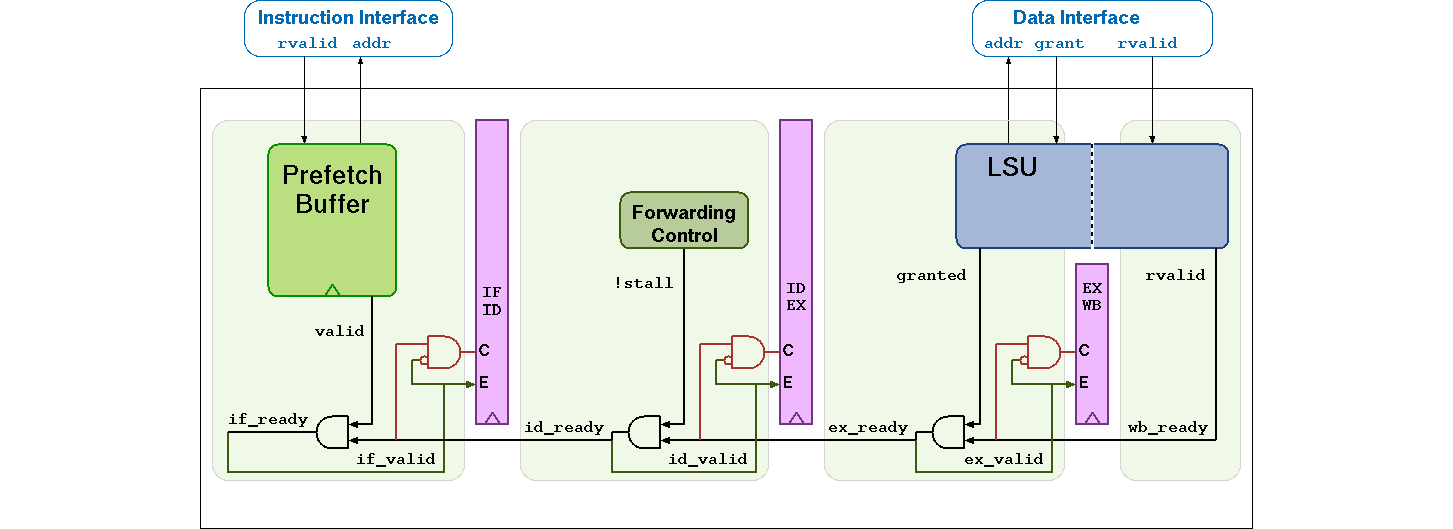

このページでパイプライン制御の図を見つけたので、以下に示します。これは4ステージのインオーダーパイプラインプロセッサです。

パイプライン制御の論理を追ってみます。EXWBは<EX>と<WB>を分離するレジスタです。通常は<EX>の結果を保持するのでEXパイプラインレジスタと呼びますが、もちろん<WB>の入力でもあるため、この設計ではそれをわかりやすいようにEXWBとしているようです。

パイプライン制御のイネーブル論理

まずイネーブル論理を見てみると、 $$ \begin{eqnarray} \text{EXWB.E}&=&\text{ex_valid}\\ &=&\text{ex_ready}\\ &=&\text{granted }\cap\text{wb_ready} \end{eqnarray} \tag{467.1} $$ これは

- <EX>が正当であるという、後段に対する有効論理、かつ

- <EX>以降のステージが受け入れ可能という、上段に対するイネーブル(ウエイトの否定)

を同時に意味します。

上段に対するウエイト信号を新たに$ex\_wait(=\text{!ex_ready})$とし、<EX>の許可信号である$\text{granted}$の逆論理を、<EX>のステージウエイトとして新たに$exs\_wait(=\text{!granted})$と名付ければ、

$$ \begin{eqnarray} ex\_wait&=&\text{!ex_ready}\\ &=&\text{!(granted }\cap\text{wb_ready)}\\ &=&\text{!granted }\cup\text{!wb_ready}\\ &=&exs\_wait \cup wb\_wait \end{eqnarray} \tag{467.2} $$ ただし、$wb\_wait=!\text{wb_ready}$

前述のように、ウエイトは、当該段のウエイトに下段のウェイト信号のORを取りながら、上段へパイプラインとは逆向きに同一サイクル中に送るので、これは正しいです。