|

14 |

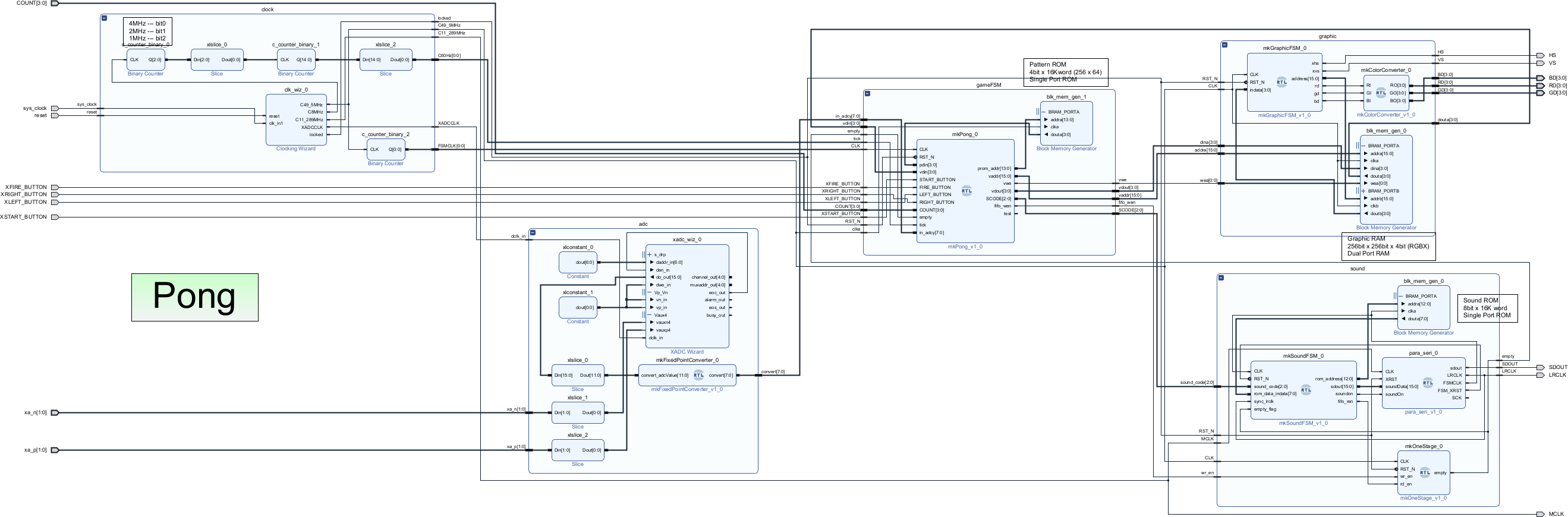

Pongの開発 (7) |

|

可変抵抗器の作成

標準ではLTSpiceに可変抵抗器は存在しないようです。そこで可変抵抗器のモデルを作成してLTSpiceに組み込んでみました。参考にさせて頂いたのはこのページ(魚拓)です。

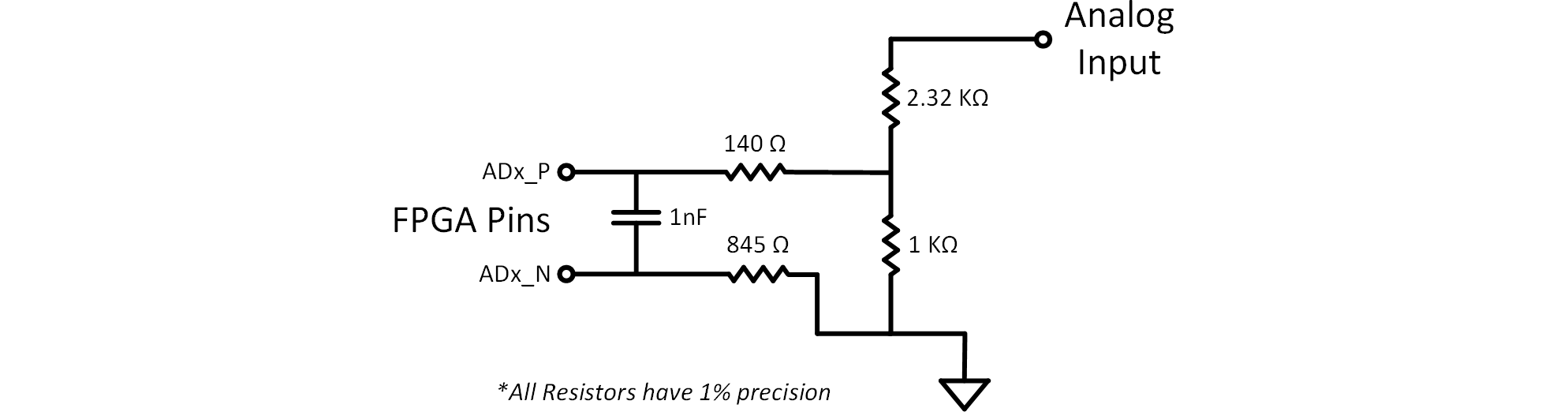

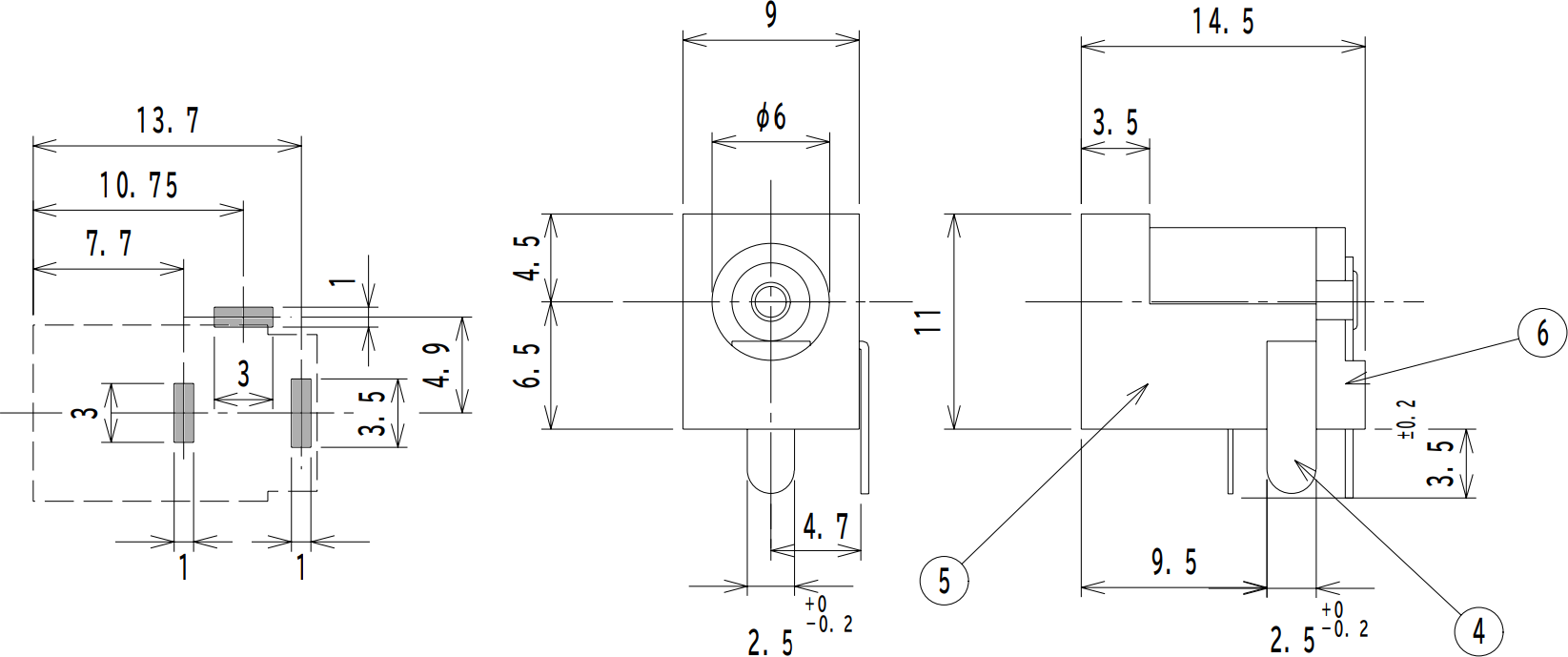

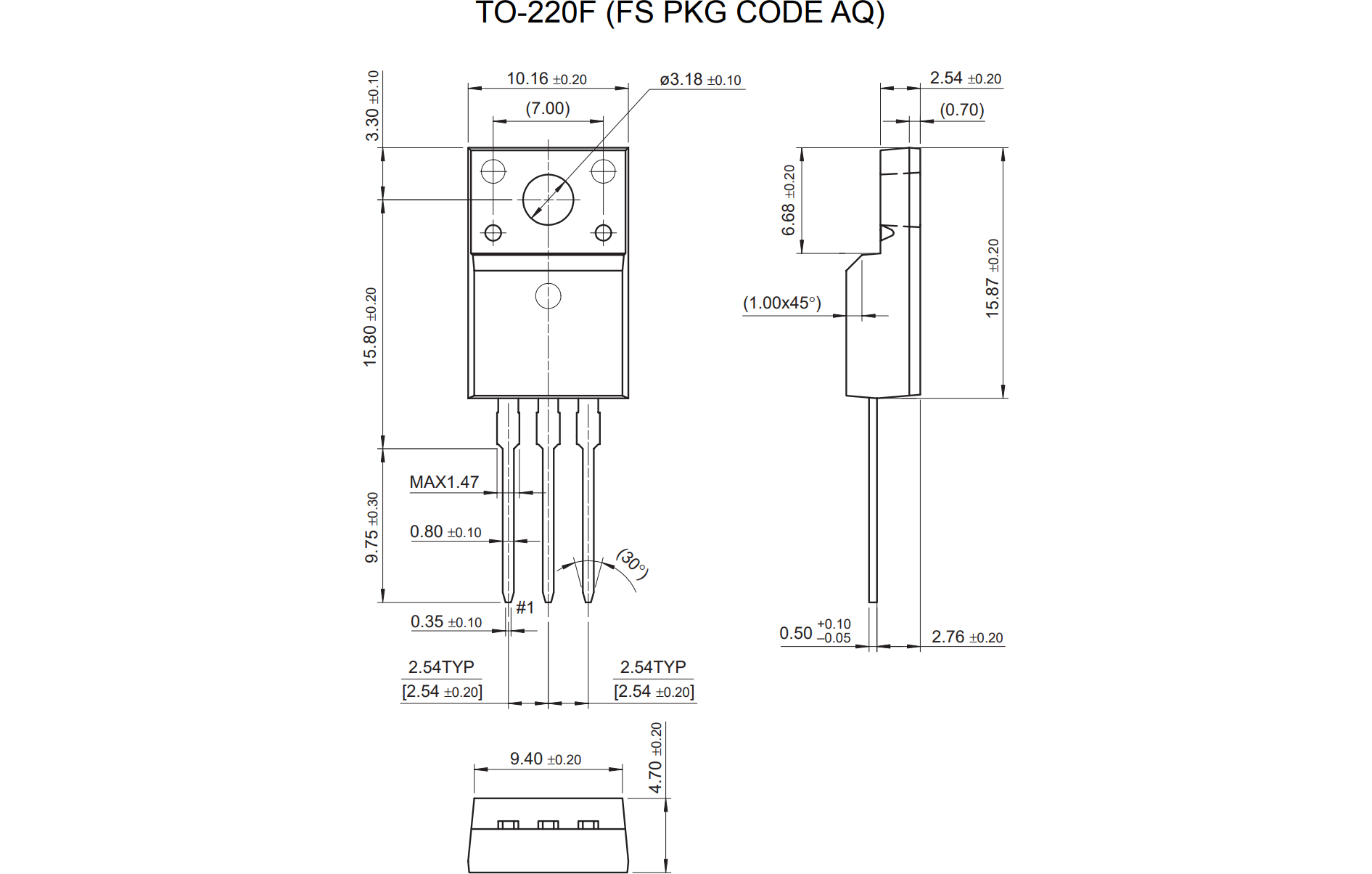

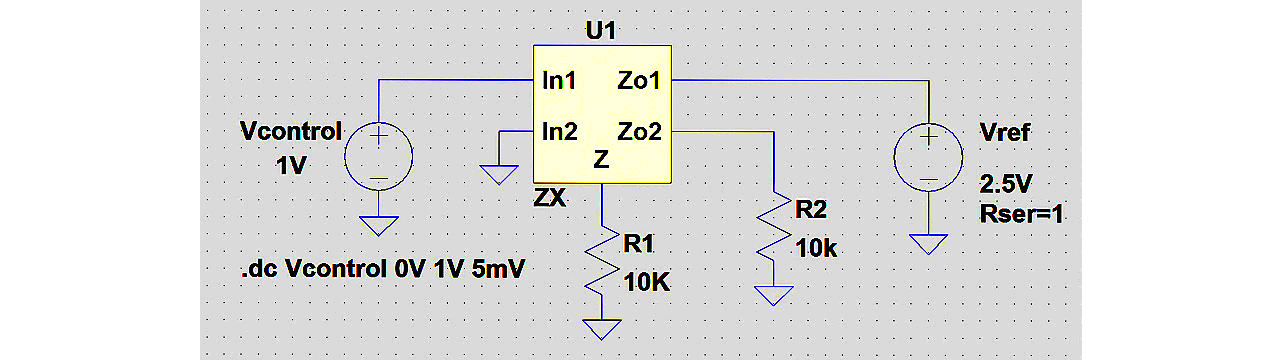

図696.1のZo1-Zo2間に0-10kΩの可変抵抗を発生させる仕様であり、インピーダンスがゼロとならないよう、電源内部に1Ω抵抗を入れています。以下はこの部品のSpice記述です。

.SUBCKT ZX In1 In2 Z Zo1 Zo2 Eout Zo1 1 POLY(2) (In1,In2) (Z,0) 0 0 0 0 1 Fcopy 0 Z Vsense 1 Rin In1 In2 1G Vsense 1 Zo2 0 .ENDS

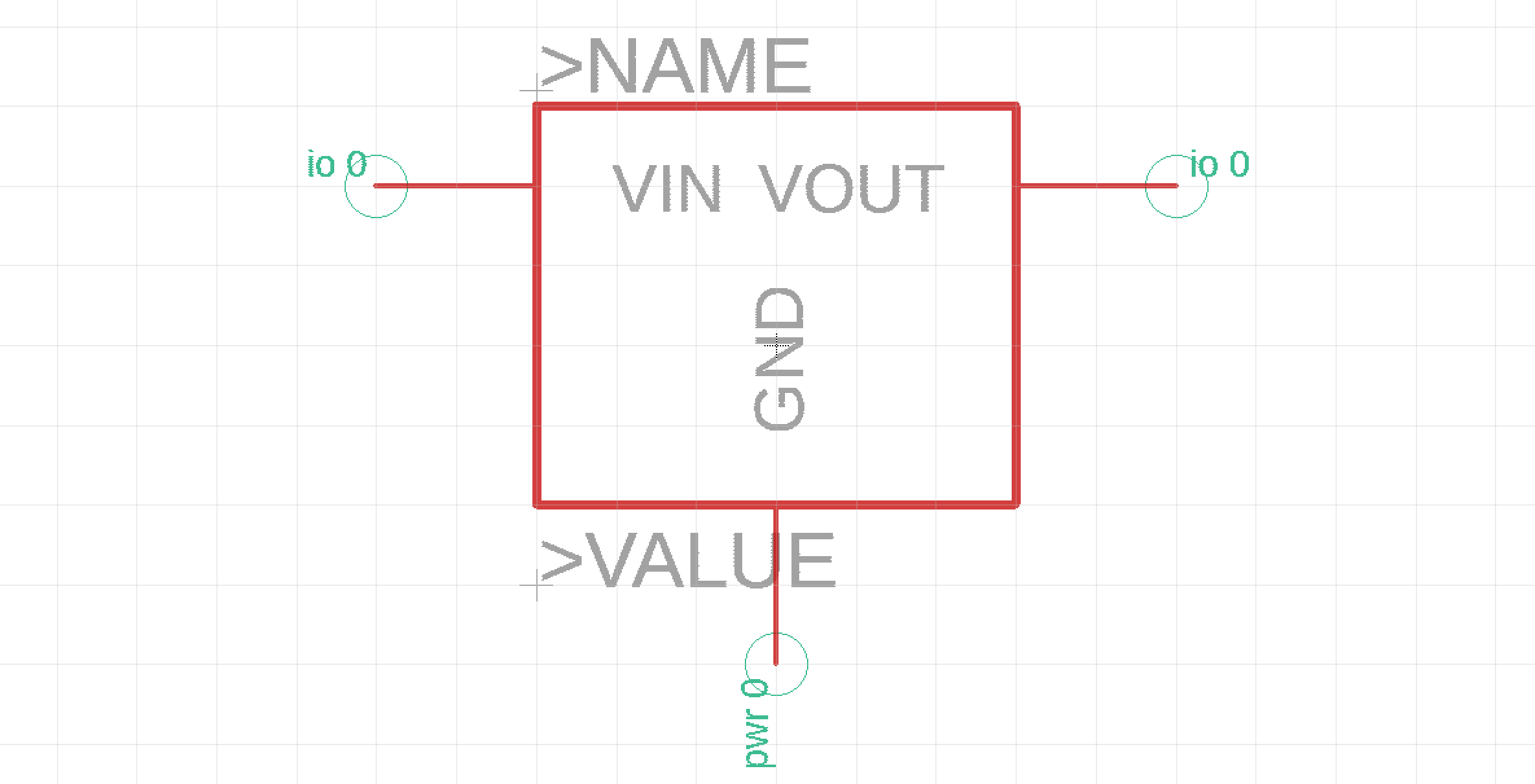

これを用いたLTSpiceにおける部品の作成法を示します。

- 上記記述をZX.subとしてC:\Users\ユーザ名\AppData\Local\LTspice\lib\subに配置

- OpenによりZX.subを開くが拡張子が制約されており対象に出ないため、全ファイルを対象として開く

- 1行目を右クリックしてCreate Symbolを行う

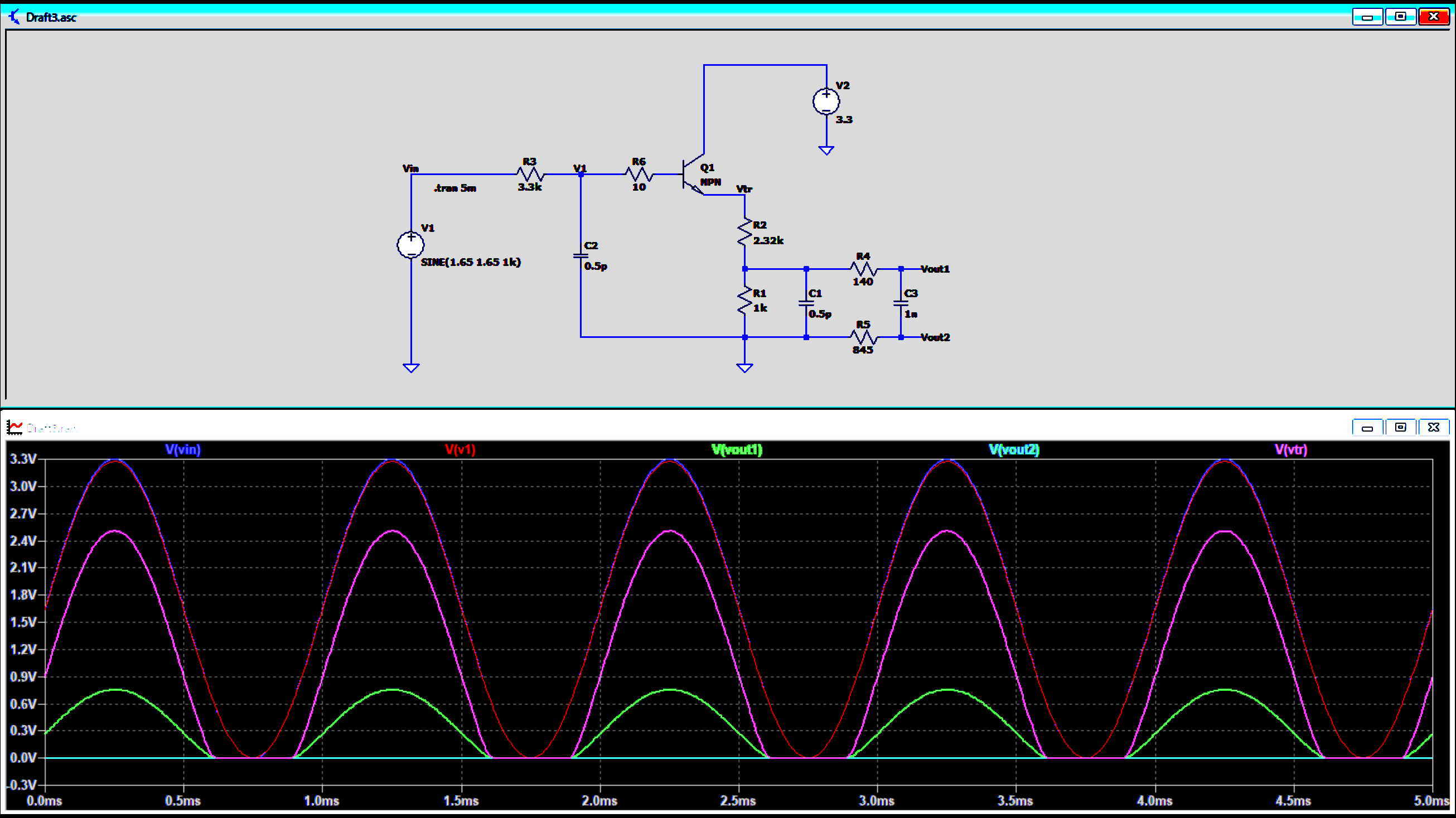

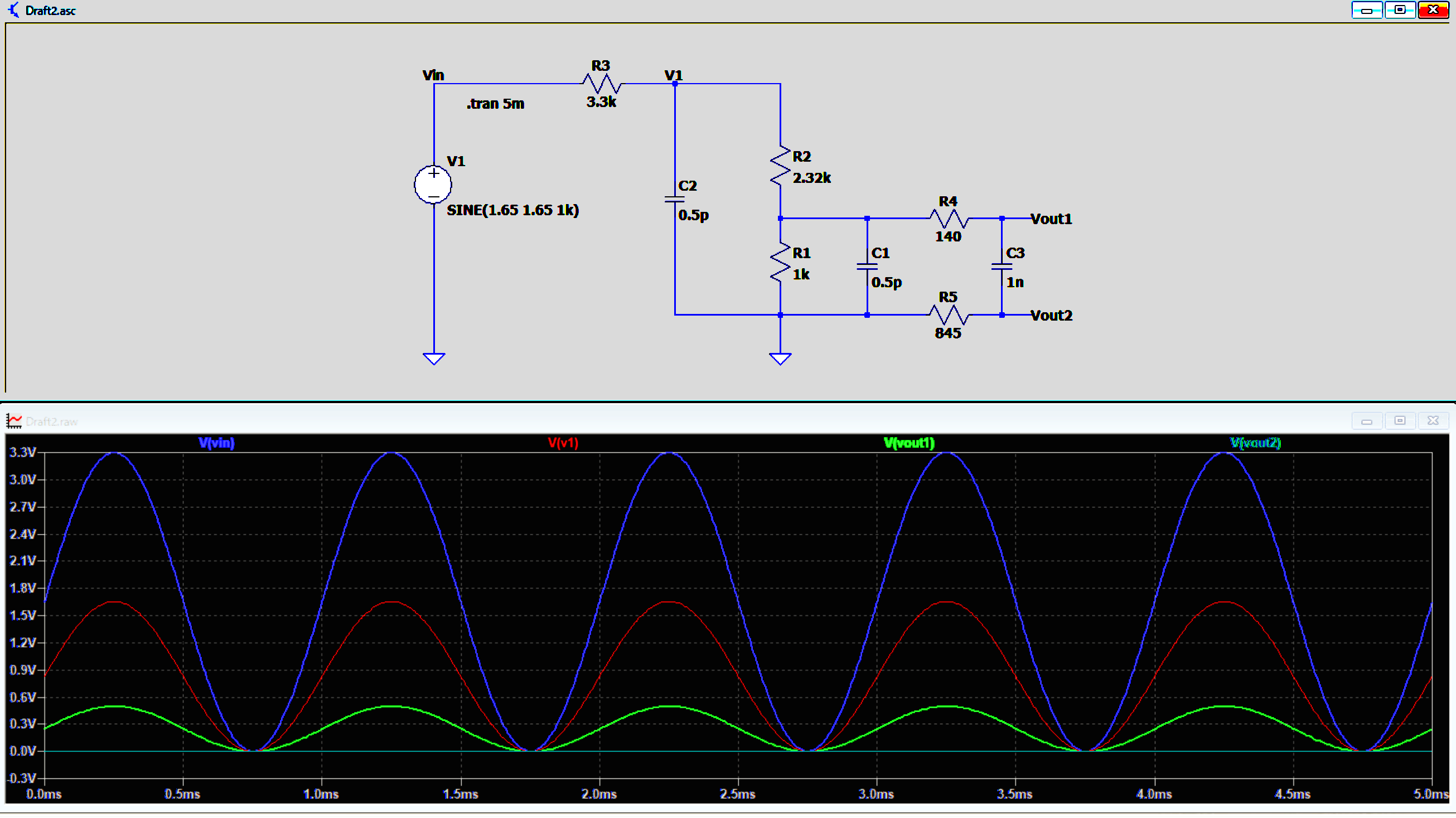

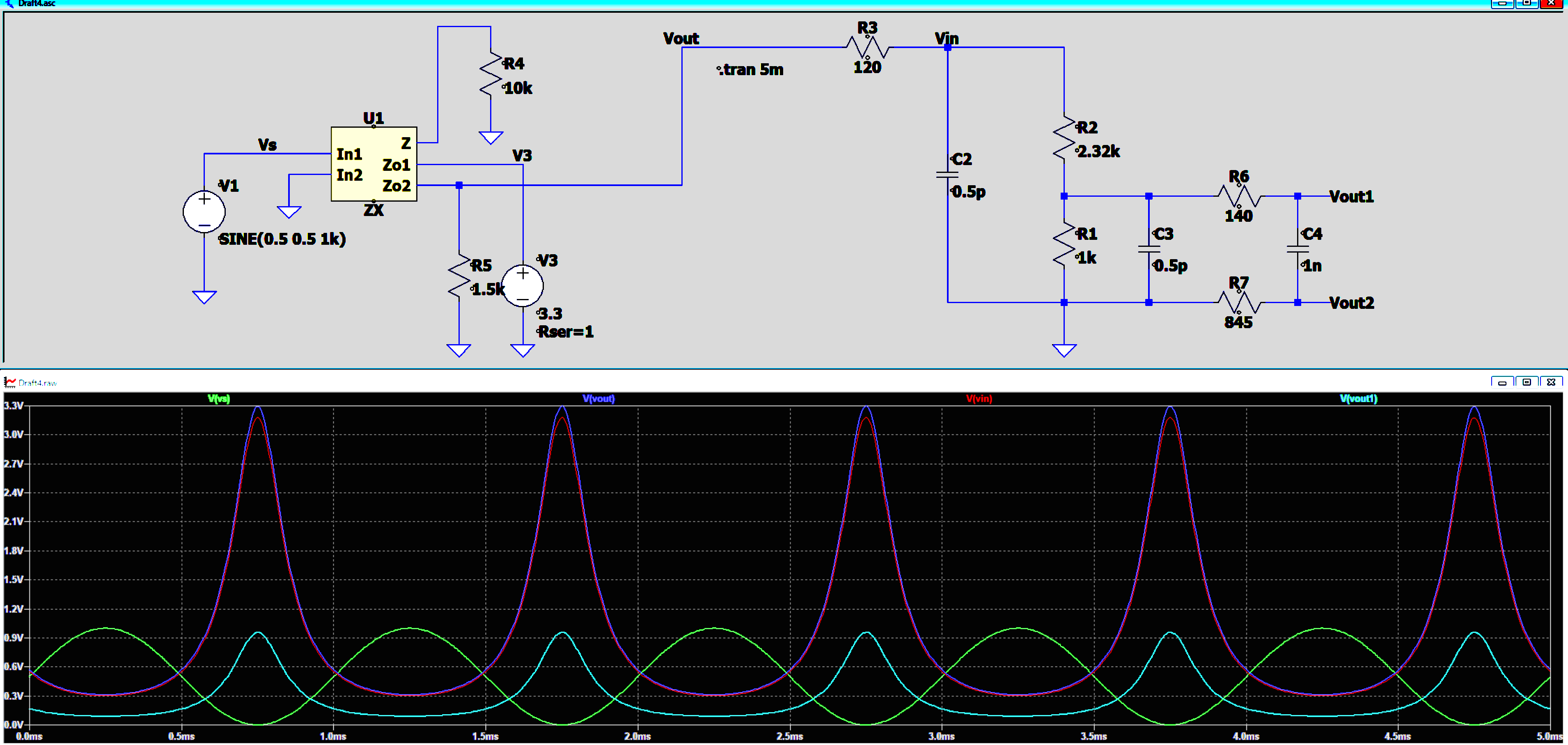

これを組み込んだ回路のシミュレーションを実施したので以下に回路と波形を示します。

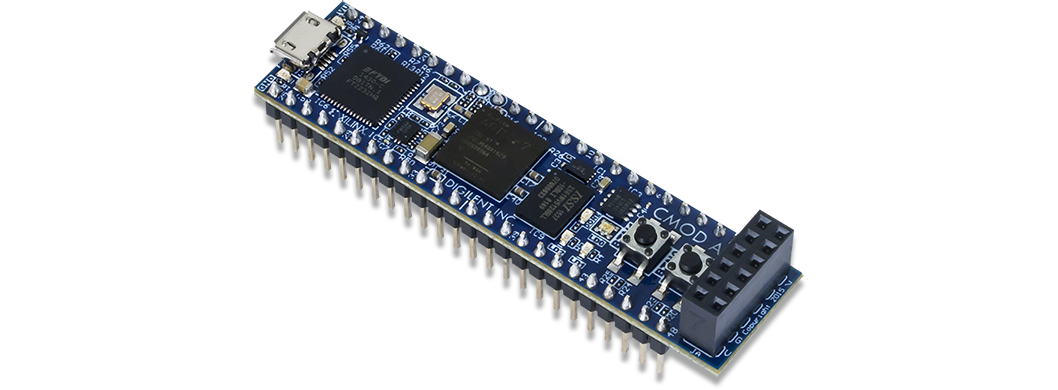

制御電圧$V_\text{1}$(グリーン)は実際には存在しない制御電圧で0~1.0Vです。Zo1とZo2の間がこれにより0~10KΩとなります。$V_\text{in}$(ブルー)は0.3~3.3Vとなり、CmodA7入力電圧$V_\text{1}$(マゼンタ)は0.3~3.2Vとなっています。ADCの入力電圧$V_\text{out1}$(ブルーグリーン)は0.07~0.94Vとなっています。ただし変化が急かもしれないので、その場合にはR5を例えば10KΩと大きくすることで調整します。

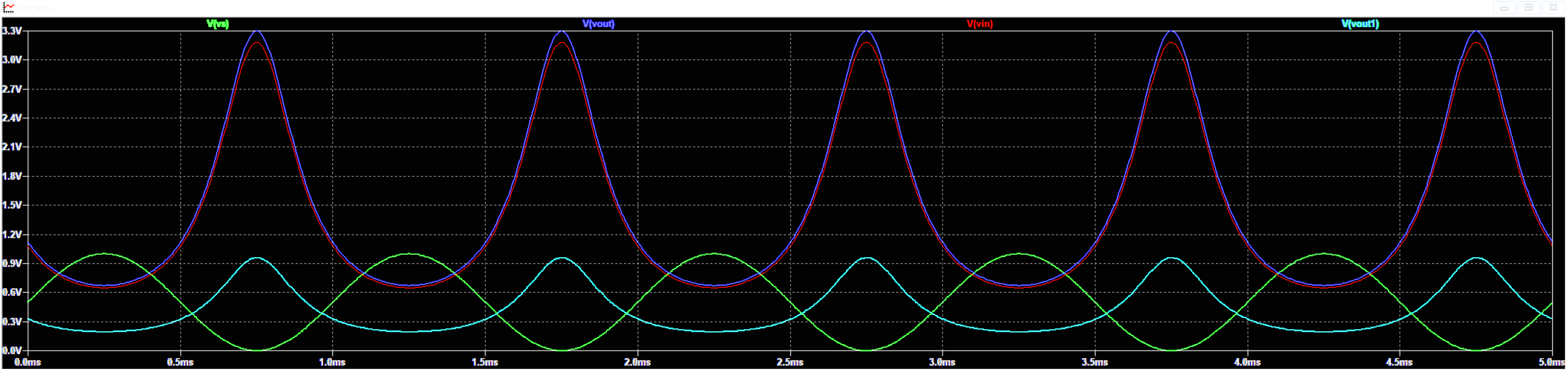

R5を10KΩとした場合、ADCの入力電圧$V_\text{out1}$(ブルーグリーン)は0.2~0.94Vと下側が上がったものの、変化が穏やかになりました。

秋月の10KΩの可変抵抗器Bを見ると可変角は最大300°だそうで、使用感を考えると可変抵抗を最大まで使うよりも角度の一部を使ったほうが使いやすそうです。そのためADC入力電圧の下側を上げて47KΩとし、回転角の60~90°くらいを使用したほうが良いかもしれません。