|

22 |

グラフィックディスプレイコントローラの設計 (3) |

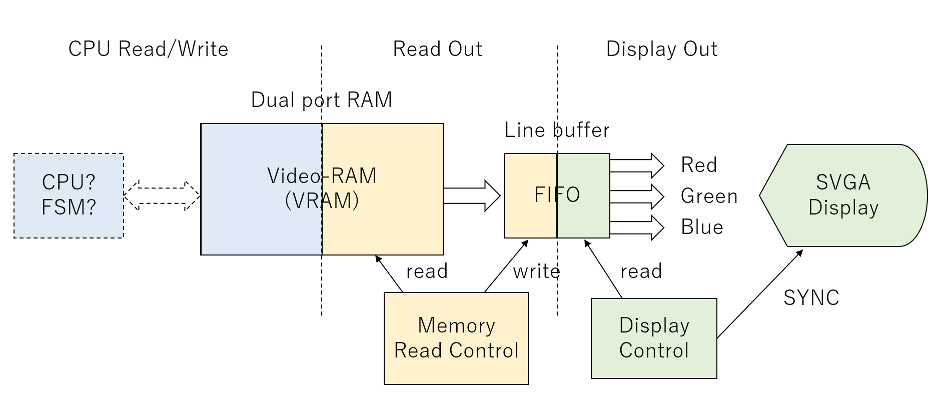

さて、デュアルポートメモリのB側をGDCの読み出し側として、どのようなタイミング設計をするかといえば、FIFOのスループットのつり合いが制約条件となります。

FIFOからみてGDCへの読み出し側は、40MHzクロックで、一ラインは1056クロックでした。この期間で800個のデータを読み出すことになるため、釣り合うためには、同じ期間で800個のデータを書き込めば良いことになります。従って、

40.0 x 800 / 1056 = 19.3939[MHz]

のクロックでVRAMから読み出し、FIFOに書き込めば良いことになります。

デュアルポートメモリのB側のみのブロック図を以下に示します。ブルーは任意のクロック周波数のクロックドメイン、オレンジは上記19.3939MHzのクロックドメイン、グリーンはドットクロックである40.0MHzのクロックドメインとなります。

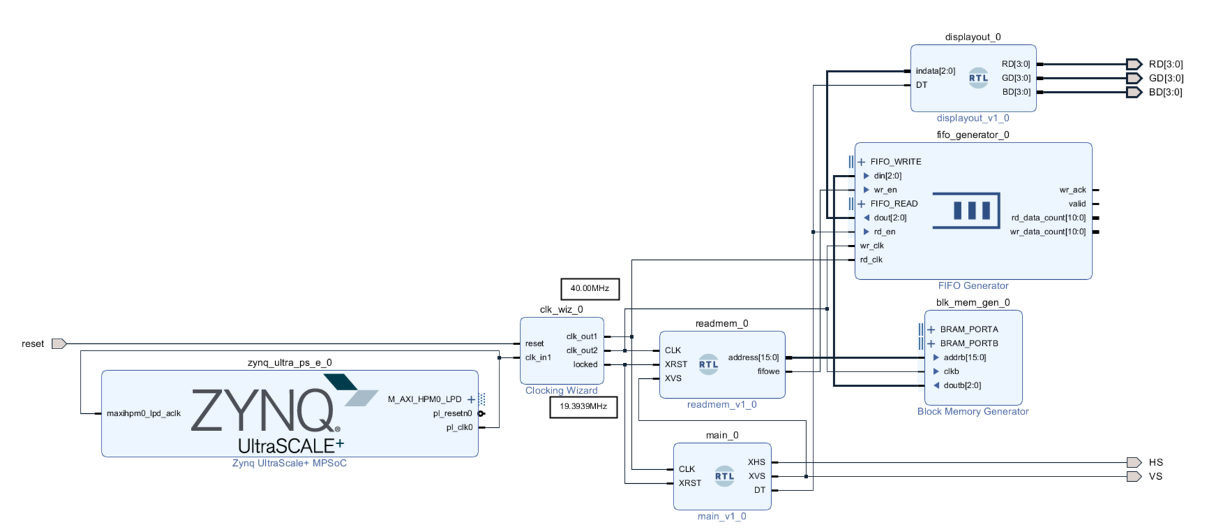

これをVivadoブロックエディタにより作成したものを以下の図に示します。